µPD178023, 178024

3.7 PLL Frequency Synthesizer

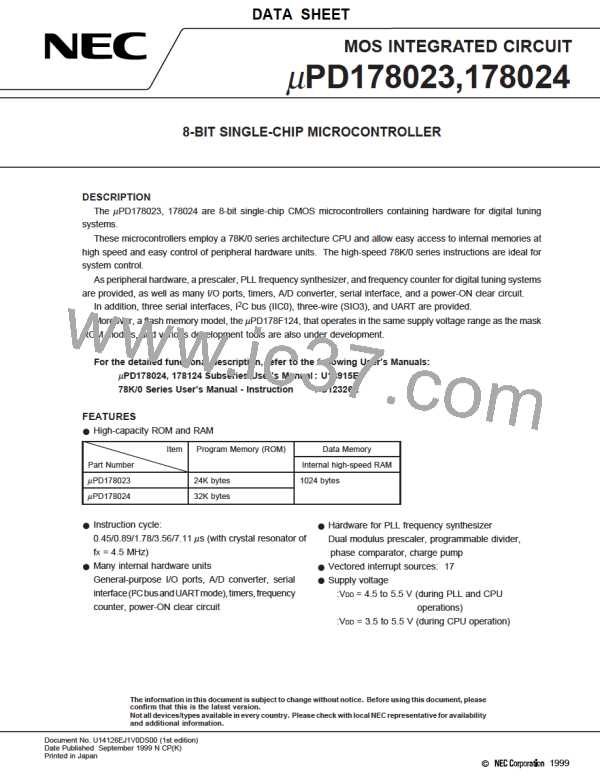

Figure 3-11. Block Diagram of PLL Frequency Synthesizer

Internal Bus

PLL Mode

Select Register

(PLLMD)

PLL

Data Transfer

Register (PLLNS)

PLL Data Register

(PLLRL, PLLRH, PLLR0)

PLL PLL

MD1 MD0

PLL

NS0

VCOH VCOL

DMD DMD

2

2

f

N

VCOH

EO1

EO0

Phase

Comparator

Mixer

Input Select

Block

Programmable

Divider

Charge

Pump

φ

(

-DET)

f

r

VCOL

Reference

Frequency

Generator

Unlock

F/F

4.5 MHz

Note

Voltage

Control

Generator

4

Note

Lowpass

Filter

PLL PLL PLL PLL

RF3 RF2 RF1 RF0

PLL

UL0

PLL Reference

Mode Register

(PLLRF)

PLL Unlock

F/F Judge Register

(PLLUL)

Internal Bus

Note External circuit.

26

Data Sheet U14126EJ1V0DS00

NEC [ NEC ]

NEC [ NEC ]