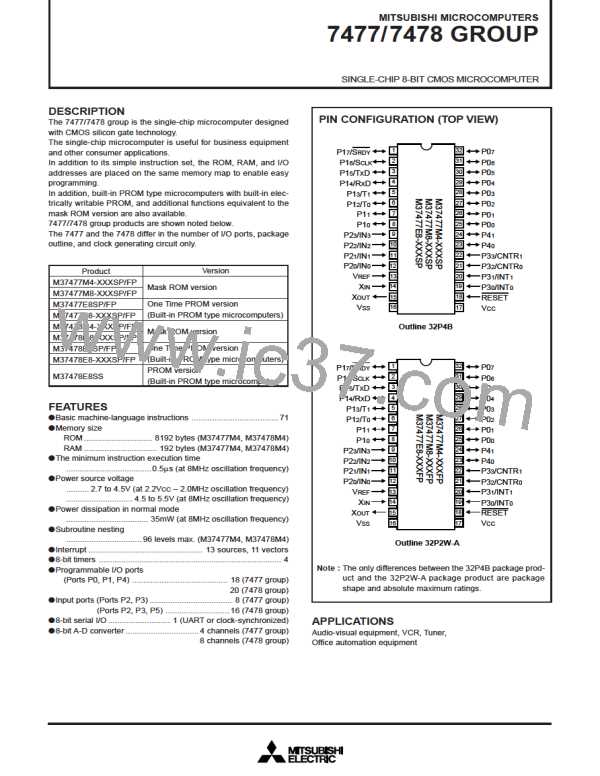

MITSUBISHI MICROCOMPUTERS

7477/7478 GROUP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b7

b0

b7

b0

Serial I/O status register

(SIOSTS: address 00E116

Serial I/O control register

(SIOCON: address 00E216

)

)

BRG count source selection bit (CSS)

0 : f(XIN)divided by 4

1 : f(XIN)divided by16

Transmit buffer empty flag (TBE)

0 : Buffer full

1 : Buffer empty

Serial I/O synchronous clock selection bit (SCS)

0 : BRG output divided by 4 (when clock synchronous

serial I/O is selected)

Receive buffer full flag (RBF)

0 : Buffer empty

1 : Buffer full

BRG output divided by 16 (when UART is selected)

1 : External clock input (when clock synchronous

serial I/O is selected )

Transmit shift completion flag (TSC)

0 : Transmit shift in progress

1 : Transmit shift completed

Overrun error flag (OE)

0 : No error

1 : Overrun error

Parity error flag (PE)

0 : No error

1 : Parity error

External clock input divided by16 (when UART is selected

)

S

RDY output enable bit (SRDY)

0 : P1

7

7

pin operates as ordinary I/O pin

pin operates as SRDY output pin

1 : P1

Transmit interrupt source selection bit (TIC)

0 : Interrupt when transmit buffer has emptied.

1 : Interrupt when transmit shift operation is completed.

Transmit enable bit (TE)

0 : Transmit disabled

1 : Transmit enabled

Framing error flag (FE)

0 : No error

1 : Framing error

Summing error flag (SE)

0 : (OE)U(PE)U(FE)=0

1 : (OE)U(PE)U(FE)=1

Receive enable bit (RE)

0 : Receive disabled

1 : Receive enabled

Not used (returns “1” when read)

Serial I/O mode selection bit (SIOM)

0 : Asynchronous serial I/O (UART)

1 : Clock synchronous serial I/O

Serial I/O enable bit (SIOE)

0 : Serial I/O disabled

b7

b0

(pins P1

I/O pins)

1 : Serial I/O enabled

(pins P1

to P1 operate as serial

I/O pins)

4 to P17 operate as ordinary

UART control register

(UARTCON: address 00E316

)

Character length selection bit (CHAS)

0 : 8 bits

1 : 7 bits

4

7

Parity enable bit (PARE)

0 : Parity checking disabled

1 : Parity checking enabled

Parity selection bit (PARS)

0 : Even parity

1 : Odd parity

Stop bit length selection bit (STPS)

0 : 1 stop bit

1 : 2 stop bits

Not used (returns “1” when read)

Fig. 12 Structure of serial I/O control registers

20

MITSUBISHI [ Mitsubishi Group ]

MITSUBISHI [ Mitsubishi Group ]