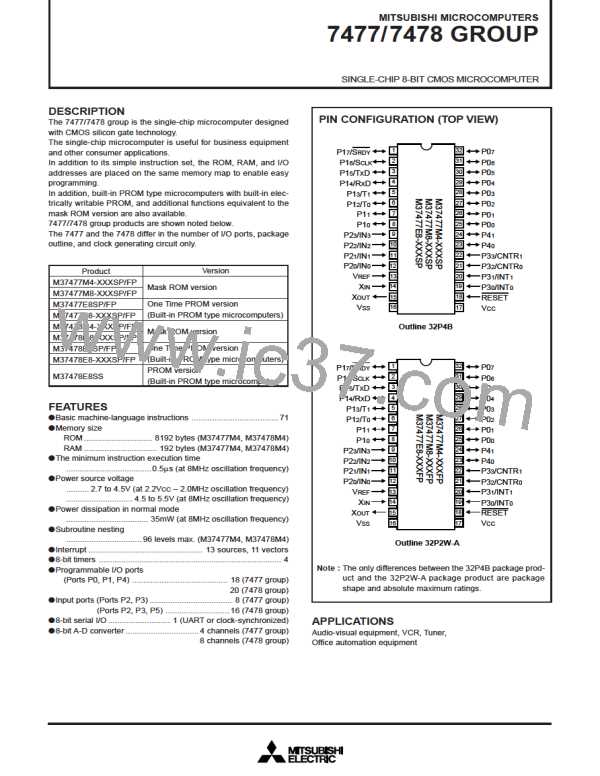

MITSUBISHI MICROCOMPUTERS

7477/7478 GROUP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Asynchronous Serial I/O (UART) Mode

Clock asynchronous serial I/O mode (UART) can be selected by

clearing the serial I/O mode selection bit of the serial I/O control

register to “0”.

Eight serial data transfer formats can be selected, and the transfer

formats used by a transmitter and receiver must be identical. The

transmit and receive shift registers each have a buffer, but the two

buffers have the same address in memory. Since the shift register

cannot be written to or read from directly, transmit data is written

to the transmit buffer, and receive data is read from the receive

buffer. The transmit buffer can also hold the next data to be trans-

mitted, and the receive buffer can hold a character while the next

character is being received.

Data bus

Serial I/O control register

P1

4

Address 00E216

RXD

RE

Address 00E016

Receive buffer register

Receive buffer full flag (RBF)

Receive interrupt request (RI)

OE

ST detection

7-bit

8-bit

Receive shift register

UART control register

SP detection

1/16

PE FE

Address 00E316

Clock control circuit

Serial I/O synchronous clock

selection bit

S

CLK

Frequency dividing ratio 1/(n+1)

f(XIN

)

1/4

P1

Baud rate generator

1/4

1/16

ST/SP/PA generation

Transmit shift completion flag (TSC)

Transmit interrupt request (TI)

TE

TIC

Transmit shift register

TXD

Character

length

selection

Transmit buffer register

Transmit buffer empty flag (TBE)

Serial I/O status register

P1

5

6

Address 00E116

bit

Address 00E016

Data bus

Fig. 10 UART serial I/O block diagram

Transmit or receive clock

Transmit buffer write signal

TBE=0

TBE=0

TSC=0

TBE=1

✽

TBE=1

TSC=1

SP

Serial output TxD

D

0

D

1

D0

D

1

ST

ST

ST

SP

1 start bit

✽

Generated at 2nd bit in 2-stop-bit mode

7 or 8 data bits

1 or 0 parity bit

1 or 2 stop bit(s)

Receive buffer read signal

RBF=0

RBF=1

SP

RBF=1

SP

Serial input RxD

ST

D

0

D

0

D1

D

1

Notes 1 : Error flag detection occurs at the same time that the RBF flag becomes “1” (at 1st stop bit during reception).

2 : The transmit interrupt (TI) can be selected to occur when either the TBE or TSC flag becomes “1,” depending on the

setting of the transmit interrupt source selection bit (TIC) of the serial I/O control register.

3 : The receive interrupt (RI) is set when the RBF flag becomes “1”.

Fig. 11 Operation of UART serial I/O function

18

MITSUBISHI [ Mitsubishi Group ]

MITSUBISHI [ Mitsubishi Group ]