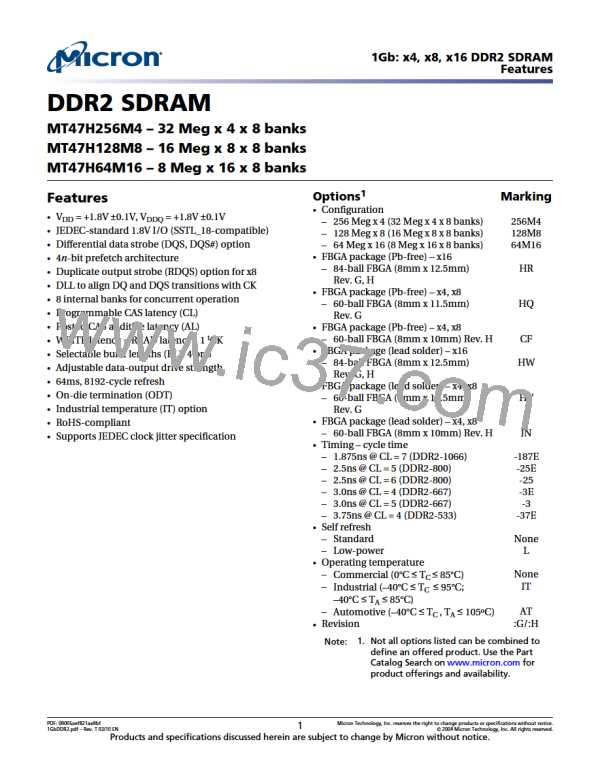

1Gb: x4, x8, x16 DDR2 SDRAM

Input Slew Rate Derating

Table 31: DDR2-667/800/1066 tDS, tDH Derating Values with Differential Strobe

All units are shown in picoseconds

DQS, DQS# Differential Slew Rate

1.8 V/ns 1.6 V/ns 1.4 V/ns

DQ

Slew

Rate

2.8 V/ns

2.4 V/ns

2.0 V/ns

1.2 V/ns

1.0 V/ns

0.8 V/ns

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

Δ

(V/ns) tDS tDH tDS tDH tDS tDH tDS tDH tDS tDH tDS tDH tDS tDH tDS tDH tDS tDH

2.0

1.5

1.0

0.9

0.8

0.7

0.6

0.5

100

67

0

63

42

0

100

67

0

63

42

0

100

67

0

63

42

0

112

79

12

7

75

54

124

91

24

19

11

2

87

66

136

103

36

31

23

14

2

99

78

36

22

5

148 111 160 123 172 135

115

48

43

35

26

14

90

48

127 102 139 114

12

24

60

55

47

38

26

0

60

46

72

67

59

50

38

12

72

58

–5

–14

–5

–14

–5

–14

–2

10

34

–13 –31 –13 –31 –13 –31

–1

–19

–7

17

29

41

–22 –54 –22 –54 –22 –54 –10 –42

–30

–18

–47

–6

6

18

–34 –83 –34 –83 –34 –83 –22 –71 –10 –59

–35

–23

–65

–11

–53

–60 –125 –60 –125 –60 –125 –48 –113 –36 –101 –24 –89 –12 –77

0.4 –100 –188 –100 –188 –100 –188 –88 –176 –76 –164 –64 –152 –52 –140 –40 –128 –28 –116

1. For all input signals the total tDS and tDH required is calculated by adding the data

Notes:

sheet value to the derating value listed in Table 31.

2. tDS nominal slew rate for a rising signal is defined as the slew rate between the last

crossing of VREF(DC) and the first crossing of VIH(AC)min. tDS nominal slew rate for a falling

signal is defined as the slew rate between the last crossing of VREF(DC) and the first cross-

ing of VIL(AC)max. If the actual signal is always earlier than the nominal slew rate line

between the shaded “VREF(DC) to AC region,” use the nominal slew rate for the derating

value (see Figure 27 (page 64)). If the actual signal is later than the nominal slew rate

line anywhere between shaded “VREF(DC) to AC region,” the slew rate of a tangent line

to the actual signal from the AC level to DC level is used for the derating value (see Fig-

ure 28 (page 64)).

3. tDH nominal slew rate for a rising signal is defined as the slew rate between the last

crossing of VIL(DC)max and the first crossing of VREF(DC). tDH nominal slew rate for a falling

signal is defined as the slew rate between the last crossing of VIH(DC)min and the first cross-

ing of VREF(DC). If the actual signal is always later than the nominal slew rate line

between the shaded “DC level to VREF(DC) region,” use the nominal slew rate for the de-

rating value (see Figure 29 (page 65)). If the actual signal is earlier than the nominal

slew rate line anywhere between the shaded “DC to VREF(DC) region,” the slew rate of a

tangent line to the actual signal from the DC level to VREF(DC) level is used for the derat-

ing value (see Figure 30 (page 65)).

4. Although the total setup time might be negative for slow slew rates (a valid input signal

will not have reached VIH[AC]/VIL[AC] at the time of the rising clock transition), a valid in-

put signal is still required to complete the transition and reach VIH(AC)/VIL(AC)

.

5. For slew rates between the values listed in this table, the derating values may be ob-

tained by linear interpolation.

6. These values are typically not subject to production test. They are verified by design and

characterization.

7. Single-ended DQS requires special derating. The values in Table 32 (page 62) are the

DQS single-ended slew rate derating with DQS referenced at VREF and DQ referenced at

the logic levels tDSb and tDHb. Converting the derated base values from DQ referenced

to the AC/DC trip points to DQ referenced to VREF is listed in Table 33 (page 62). Ta-

ble 33 provides the VREF-based fully derated values for the DQ (tDSa and tDHa) for

PDF: 09005aef821ae8bf

1GbDDR2.pdf – Rev. T 02/10 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice.

61

© 2004 Micron Technology, Inc. All rights reserved.

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]