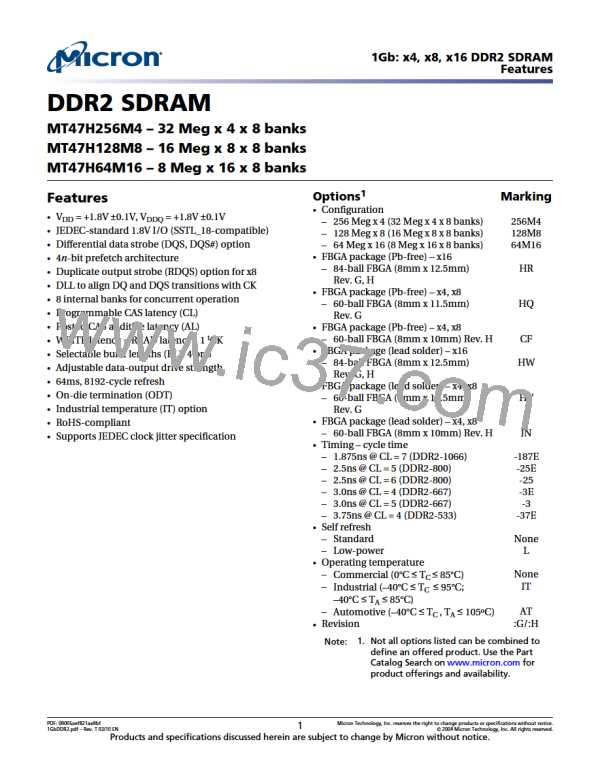

1Gb: x4, x8, x16 DDR2 SDRAM

Input Slew Rate Derating

Figure 23: Nominal Slew Rate for tIS

CK

CK#

t

t

t

t

IH

IH

IS

IS

V

DDQ

V

IH(AC)min

V

to AC

region

REF

V

IH(DC)min

Nominal

slew rate

V

REF(DC)

Nominal

slew rate

V

V

IL(DC)max

VREF to AC

region

IL(AC)max

V

SS

ΔTF

ΔTR

V

(DC) - V

IL(AC)max

V

- V

Setup slew rate

rising signal

REF

Setup slew rate

falling signal

IH(AC)min REF(DC)

=

=

ΔTF

Δ

TR

Figure 24: Tangent Line for tIS

CK

CK#

t

t

t

t

IH

IH

IS

IS

V

DDQ

V

V

IH(AC)min

V

to AC

region

REF

Nominal

line

IH(DC)min

Tangent

line

V

REF(DC)

Tangent

line

V

V

IL(DC)max

Nominal

line

V

to AC

region

REF

IL(AC)max

ΔTF

ΔTR

V

SS

Tangent line (V

- V

)

Setup slew rate

rising signal

IH[AC]min

REF[DC]

=

ΔTR

PDF: 09005aef821ae8bf

1GbDDR2.pdf – Rev. T 02/10 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice.

58

© 2004 Micron Technology, Inc. All rights reserved.

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]