TC7109/A

Zero Crossing Occurs

Zero Crossing Detected

Integrator Output

Internal Clock

Internal Latch

Status Output

Mode Input

UART

Norm

Terminates

UART Mode

Send

Sensed

Send

Sensed

Send

Sensed

Internal Mode

Send Input (UART TBRE)

CE/LOAD Output (UART TBRL)

HBEN

High Byte Data

LBEN

Data Valid

Low Byte Data

Data Valid

Three-State High-Impedance

=

= Don't Care

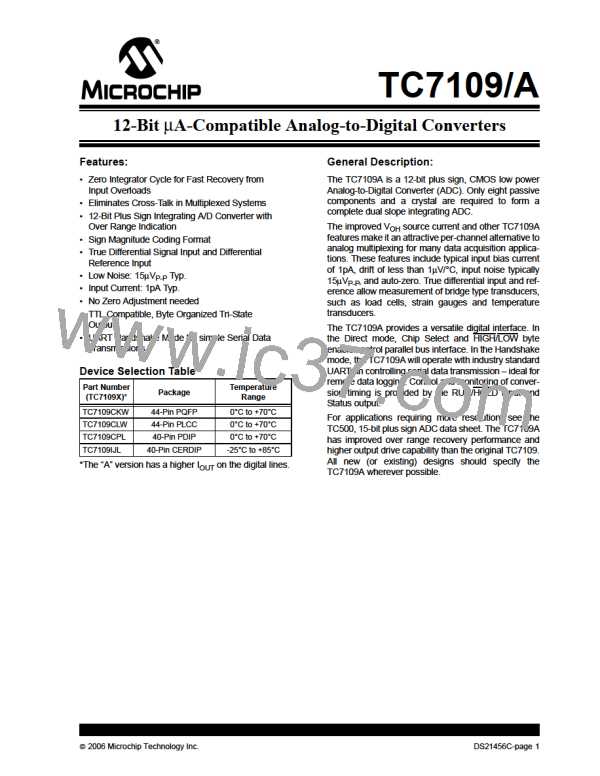

FIGURE 3-8:

TC7109A Handshake – Typical UART Interface Timing

Zero Crossing Occurs

Zero Crossing Detected

Positive Transiton causes

Entry into UART Mode

Status Output unchanged

in UART Mode

Latch Pulse inhibited in UART Mode

Internal Clock

Internal Latch

Status Output

DE Phase III

Mode Input

UART

Norm

Terminates

UART Mode

Send

Sensed

Send

Sensed

Send

Sensed

Internal Mode

Send Input

CE/LOAD as Output

HBEN

High Byte Data

LBEN

Data Valid

Low Byte Data

Data Valid

Three-State

High-Impedance

Three-State

=

=

= Don't Care

with Pull-up

FIGURE 3-9:

TC7109A Handshake Triggered by Mode Input

DS21456C-page 14

© 2006 Microchip Technology Inc.

MICROCHIP [ MICROCHIP ]

MICROCHIP [ MICROCHIP ]