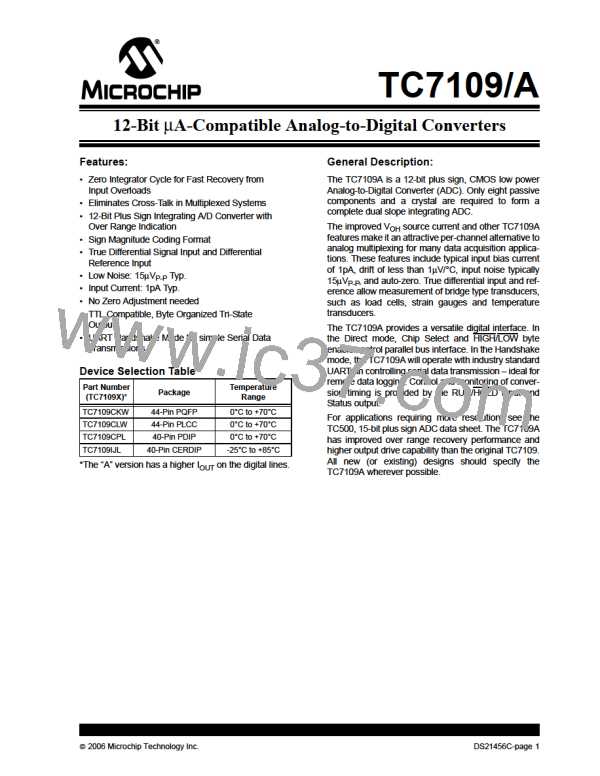

TC7109/A

Figure through Figure give practical circuits utilizing

the parallel three-state output capabilities of the

TC7109A. Figure shows parallel interface to the 8748/

49 systems via an 8255 PPI, where the TC7109A data

outputs are active at all times. This interface can be

used in a read-after-update sequence, as shown in

Figure . The data is accessed by the high-to-low

transition of the Status driving an interrupt to the

microcontroller.

4.0

4.1

INTERFACING

Direct Mode

Combinations of chip enable and byte enable control

signals, which may be used when interfacing the

TC7109A to parallel data lines, are shown in Figure .

The CE/LOAD input may be tied low, allowing either byte

to be controlled by its own enable (see Figure (A)).

Figure (B) shows the HBEN and LBEN as flag inputs,

and CE/LOAD as a master enable, which could be the

READ strobe available from most microprocessors.

Figure (C) shows a configuration where the two byte

enables are connected together. The CE/LOAD is a

chip enable, and the HBEN and LBEN may be used as

a second chip enable, or connected to ground. The 14

data outputs will be enabled at the same time. In the

direct MODE, SEND should be tied to V+.

The RUN/HOLD input is also used to initiate

conversions under software control.

Direct interfacing to most microcontroller busses is

easily accomplished through the three-state output of

the TC7109A.

Figure 4-8 is a typical connection diagram. To ensure

requirements for setup and hold times, minimum pulse

widths, and the drive limitations on long busses are

met, it is necessary to carefully consider the system

timing in this type of interface. This type of interface is

used when the memory peripheral address density is

low, providing simple address decoding. Interrupt

handling can be simplified by using an interface to

reduce the component count.

Figure shows interfacing several TC7109A’s to a bus,

ganging the HBEN and LBEN signals to several

converters together, and using the CE/LOAD input to

select the desired converter.

Chip Select 1

Chip Select

GND

A. GND

B. GND

C.

MODE CE/LOAD

MODE

CE/LOAD

MODE CE/LOAD

B

- B

B - B

9 12

POL, OR

9

12

POL, OR

B

- B

12

POL, OR

6

6

1

14

TC7109A

B

TC7109A

B

TC7109A

- B

8

- B

8

8

1

8

1

Analog In

Analog In

Analog In

RUN/HOLD

LBEN

RUN/HOLD

LBEN

RUN/HOLD

LBEN

Convert

Convert

Convert

HBEN

HBEN

HBEN

GND or

Chip Select 2

Control

Byte Flags

FIGURE 4-1:

Direct Mode Chip and Byte Enable Combination

© 2006 Microchip Technology Inc.

DS21456C-page 17

MICROCHIP [ MICROCHIP ]

MICROCHIP [ MICROCHIP ]