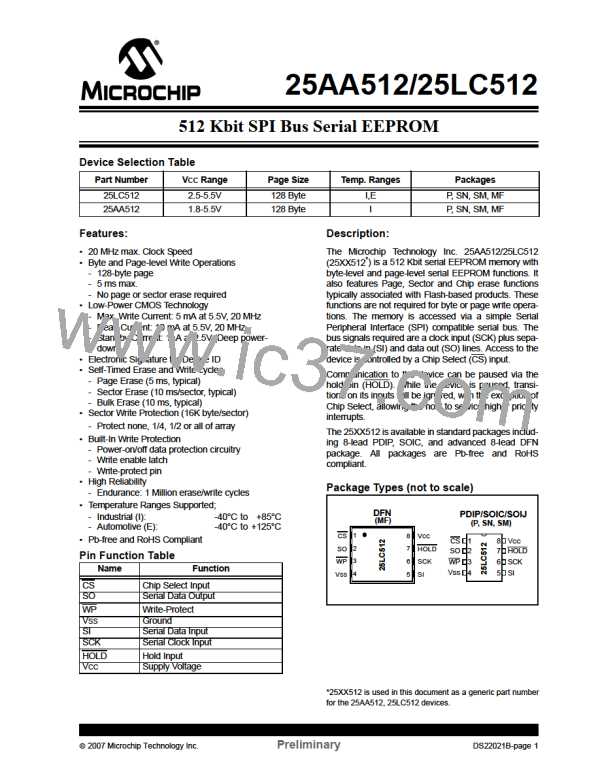

25AA512/25LC512

2.11 DEEP POWER-DOWN MODE

Deep Power-Down mode of the 25XX512 is its lowest

power consumption state. The device will not respond

to any of the Read or Write commands while in Deep

Power-Down mode, and therefore it can be used as an

additional software write protection feature.

All instructions given during Deep Power-Down mode

are ignored except the Read Electronic Signature

command (RDID). The RDID command will release

the device from Deep power-down and outputs the

electronic signature on the SO pin, and then returns

the device to Standby mode after delay (TREL

)

The Deep Power-Down mode is entered by driving CS

low, followed by the instruction code (Figure 2-11) onto

the SI line, followed by driving CS high.

Deep Power-Down mode automatically releases at

device power-down. Once power is restored to the

device it will power-up in the Standby mode.

If the CS pin is not driven high after the eighth bit of the

instruction code has been given, the device will not

execute Deep power-down. Once the CS line is driven

high there is a delay (TDP) before the current settles to

its lowest consumption.

FIGURE 2-11:

DEEP POWER-DOWN SEQUENCE

CS

0

1

2

3

4

5

6

7

SCK

1

0

1

1

1

0

0

1

SI

High-Impedance

SO

© 2007 Microchip Technology Inc.

Preliminary

DS22021B-page 17

MICROCHIP [ MICROCHIP ]

MICROCHIP [ MICROCHIP ]