MX25L8005

DEVICE OPERATION

1. Before a command is issued, status register should be checked to ensure device is ready for the intended operation.

2. When incorrect command is inputted to this LSI, this LSI becomes standby mode and keeps the standby mode until

next CS# falling edge. In standby mode, SO pin of this LSI should be High-Z.

3. When correct command is inputted to this LSI, this LSI becomes active mode and keeps the active mode until next

CS# rising edge.

4. Input data is latched on the rising edge of Serial Clock(SCLK) and data shifts out on the falling edge of SCLK. The

difference of SPI mode 0 and mode 3 is shown as Figure 2.

5. Forthefollowinginstructions:RDID,RDSR,READ,FAST_READ,RESandREMStheshifted-ininstructionsequence

is followed by a data-out sequence. After any bit of data being shifted out, the CS# can be high. For the following

instructions:WREN,WRDI,WRSR,SE,BE,CE,PP,RDPandDPtheCS#mustgohighexactlyatthebyteboundary;

otherwise, the instruction will be rejected and not executed.

6. DuringtheprogressofWriteStatusRegister,Program,Eraseoperation,toaccessthememoryarrayisneglectedand

not affect the current operation of Write Status Register, Program, Erase.

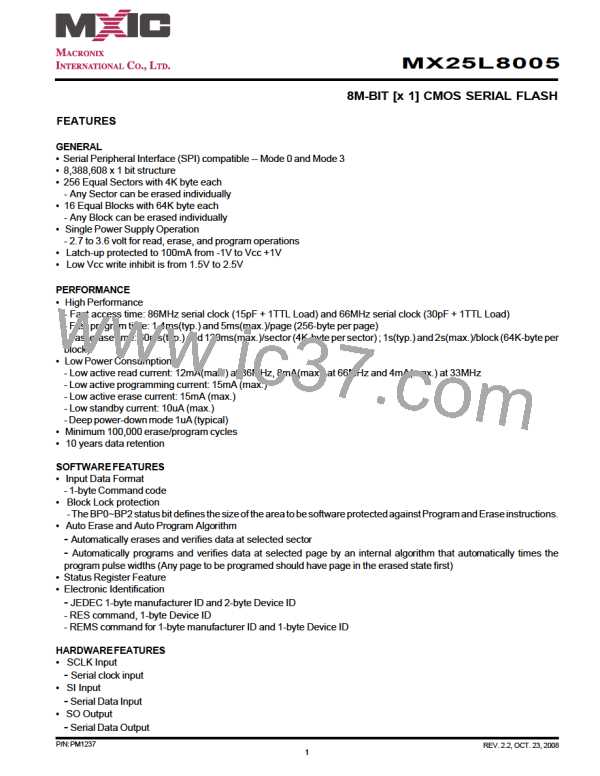

Figure 2. SPI Modes Supported

CPOL CPHA

shift in

shift out

SCLK

SCLK

(SPI mode 0)

(SPI mode 3)

0

1

0

1

SI

MSB

SO

MSB

Note:

CPOL indicates clock polarity of SPI master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not

transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which SPI mode is

supported.

P/N:PM1237

REV. 2.2, OCT. 23, 2008

9

Macronix [ MACRONIX INTERNATIONAL ]

Macronix [ MACRONIX INTERNATIONAL ]