LANSDALE Semiconductor, Inc.

ML145156

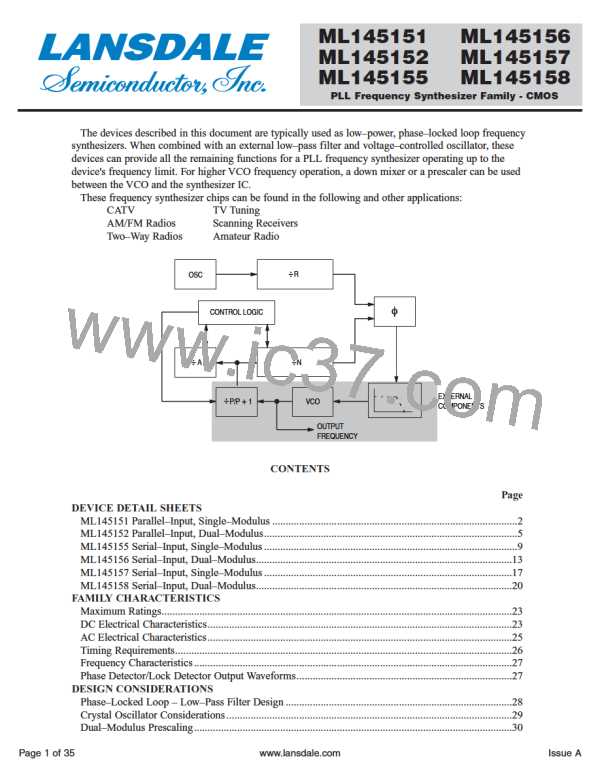

ML145156

OUTPUT PINS

respective programmed values, and the above sequence repeat-

ed. This provides for a total programmable divide value (N ) =

T

PDout

N • P + A where P and P + 1 represent the dual–modulus

prescaler divide values respectively for high and low MC lev-

els, N the number programmed into the ÷ N counter, and A the

number programmed into the ÷ A counter.

Phase Detector A Output (Pin 6)

Three–state output of phase detector for use as loop–error

signal. Double–ended outputs are also available for this pur-

pose (see φ and φ ).

V

R

LD

Frequency f > f or f Leading: Negative Pulses

V

R

V

V

Lock Detector Output (Pin 9)

Frequency f < f or f Lagging: Positive Pulses

V

V

R

R

Frequency f = f and Phase Coincidence: High–Imped-

Essentially a high level when loop is locked (f , f of same

R V

ance State

phase and frequency). LD pulses low when loop is out of lock.

φR, φV

SW1, SW2

Band Switch Outputs (Pins 14, 15)

Phase Detector B Outputs (Pins 4, 3)

These phase detector outputs can be combined externally for

a loop–error signal. A single–ended output is also available for

SW1 and SW2 provide latched open–drain outputs corre-

sponding to data bits numbers one and two. These outputs can

be tied through external resistors to voltages as high as 15 V,

this purpose (see PD ).

out

If frequency f is greater than f or if the phase of f is

independent of the V

supply voltage. These are typically

V

R

V

DD

leading, then error information is provided by φ pulsing low.

used for band switch functions. A logic 1 causes the output to

assume a high–impedance state, while a logic 0 causes the out-

put to be low.

V

φ remains essentially high.

R

If the frequency f is less than f or if the phase of f is

V

R

V

lagging, then error information is provided by φ pulsing low.

R

φ

remains essentially high.

REF

out

V

If the frequency of f = f and both are in phase, then both

Buffered Reference Oscillator Output (Pin 17)

V

R

φ

and φ remain high except for a small minimum time

V

R

Buffered output of on–chip reference oscillator or externally

provided reference–input signal.

period when both pulse low in phase.

MC

POWER SUPPLY

Dual–Modulus Prescale Control Output (Pin 8)

Signal generated by the on–chip control logic circuitry for-

controlling an external dual–modulus prescaler. The MC level-

will be low at the beginning of a count cycle and will remain-

low until the ÷ A counter has counted down from its pro-

grammed value. At this time, MC goes high and remains high-

until the ÷ N counter has counted the rest of the way down-

from its programmed value (N – A additional counts since

both ÷ N and ÷ A are counting down during the first portion of

the cycle). MC is then set back low, the counters preset to their

V

DD

Positive Power Supply (Pin 5)

The positive power supply potential. This pin may range

from + 3 to + 9 V with respect to V

.

SS

V

SS

Negative Power Supply (Pin 7)

The most negative supply potential. This pin is usually-

ground.

Page 15 of 35

www.lansdale.com

Issue A

LANSDALE [ LANSDALE SEMICONDUCTOR INC. ]

LANSDALE [ LANSDALE SEMICONDUCTOR INC. ]