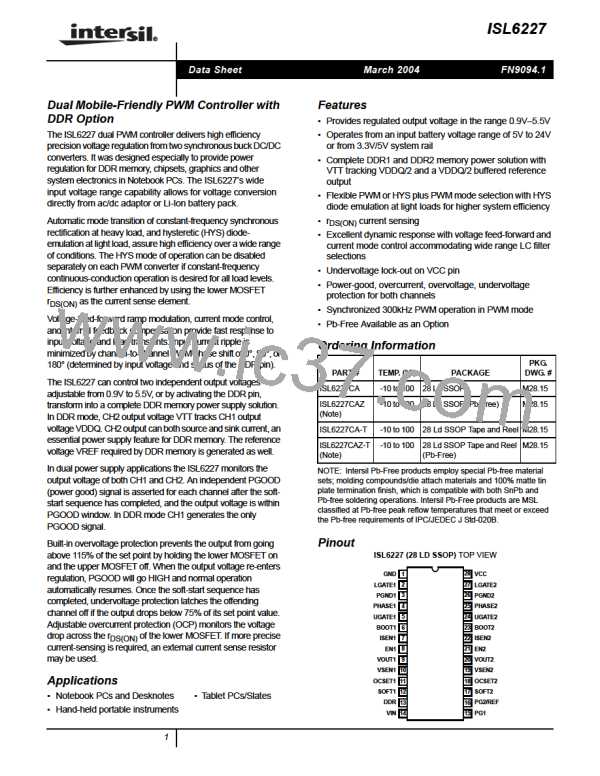

Block Diagram

BOOT1

UGATE1

PHASE1

PGND1

LGATE1

VCC

BOOT2

UGATE2

PHASE2

PGND2

LGATE2

VCC

PG1

EN1 VOUT1

VCC GND

VOUT2 EN2 REF/PG2

DDR=1

DDR=0

ADAPTIVE DEAD-TIME

DIODE EMULATION

V/I SAMPLE TIMING

PWM/HYS TRANSITION

ADAPTIVE DEAD-TIME

DIODE EMULATION

V/I SAMPLE TIMING

PWM/HYS TRANSITION

POR

MODE CHANGE COMP 1

MODE CHANGE COMP 2

ENABLE

SAME STATE FOR

8 CLOCK CYCLES

SAME STATE FOR

8 CLOCK CYCLES

BIAS SUPPLIES

REFERENCE

FAULT LATCH

SOFT START

REQUIRED TO CHANGE

PWM OR HYS MODE

REQUIRED TO CHANGE

PWM OR HYS MODE

HYSTERETIC COMPARATOR 2

HYSTERETIC COMPARATOR 1

∆V

=15mV

15pF

∆V

=15mV

HYS

HYS

OV UV

OV UV

PGOOD

PGOOD

15pF

1MΩ

DDR MODE

CONTROL

1MΩ

VOLTS/SEC

CLAMP

VOLTS/SEC

CLAMP

500kΩ

500kΩ

VSEN2

300kΩ

300kΩ

VSEN1

1.25pF

1.25pF

OC1 DDR OC2

4.4kΩ

4.4kΩ

(200kΩ, DDR=1)

PWM1

PWM2

SOFT2

ERROR AMP 1

ERROR AMP 2

+

0.9V

REF

DDR=0

DUTY CYCLE RAMP GENERATOR

PWM CHANNEL PHASE CONTROL

DDR=1

ISEN2

SOFT1

ISEN1

+

0.9V

REF

DDR EN1 EN2

VIN

φ

CH1CH2

180º

140Ω

140Ω

0

1

1

⇔

0

24.0V

<

<

90º

4.2 VIN 24.0V

VIN < 4.2

CURRENT

SAMPLE

CURRENT

SAMPLE

1

1

1

CURRENT

SAMPLE

CURRENT

SAMPLE

0º

OCSET2

DDR=1

OCSET1

DDR=0

0.9V REFERENCE

0.9V REFERENCE

+

+

OC1

OC2

1/33.1

ISEN1

1/2.9

OCSET1

1/2.9

OCSET2

1/33.1

ISEN2

VIN

DDR

VCC

SAME STATE FOR

8 CLOCK CYCLES

SAME STATE FOR

8 CLOCK CYCLES

DDR VTT

DDR VREF

REFERENCE

BUFFER AMP

REQUIRED TO LATCH

OVERCURRENT FAULT

REQUIRED TO LATCH

OVERCURRENT FAULT

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]