1-Gbit P30 Family

Figure 39.

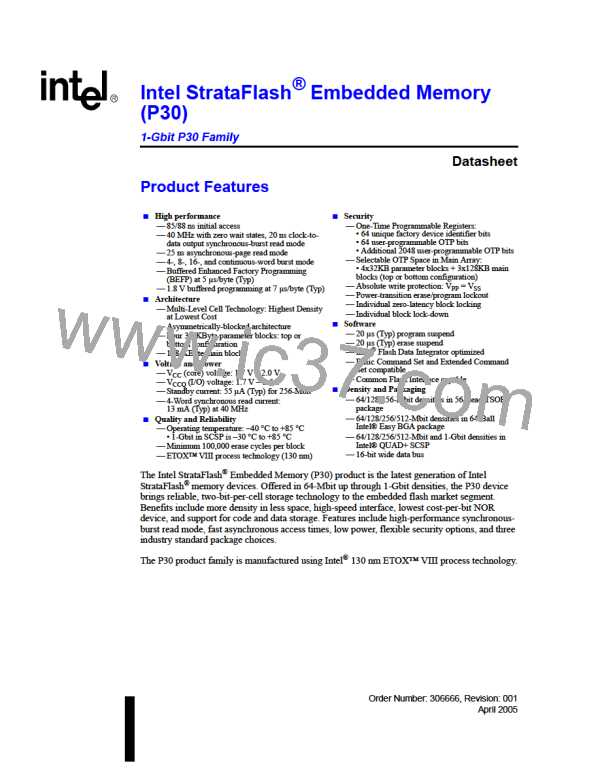

Write State Machine—Next State Table (Sheet 6 of 6)

Output Next State Table

Command Input to Chip and resulting Output Mux Next State

Lock

Block

Confirm (8) Confirm

Lock-Down

OTP

Setup (4)

Write CR

Illegal Cmds or

BEFP Data (1)

Block Address

(?WA0)

Block

WSM

(8)

Confirm

(8)

Operation

Completes

Current chip state

(C0H)

(01H)

(2FH)

(03H)

(FFFFH)

(all other codes)

BEFP Setup,

BEFP Pgm & Verify

Busy,

Erase Setup,

OTP Setup,

BP: Setup, Load 1,

Load 2, Confirm,

Word Pgm Setup,

Word Pgm Setup in

Erase Susp,

Status Read

BP Setup, Load1,

Load 2, Confirm in

Erase Suspend

Lock/CR Setup,

Lock/CR Setup in

Erase Susp

Array

Read

Status Read

Status Read

Output does

not change.

OTP Busy

Ready,

Erase Suspend,

BP Suspend

BP Busy,

Word Program

Busy,

Erase Busy,

BP Busy

Status

Read

Output does not

change.

Output does not change.

Array Read

BP Busy in Erase

Suspend

Word Pgm

Suspend,

Word Pgm Busy in

Erase Suspend,

Pgm Suspend In

Erase Suspend

Notes:

1.

2.

3.

4.

"Illegal commands" include commands outside of the allowed command set (allowed commands: 40H [pgm], 20H [erase],

etc.)

If a "Read Array" is attempted from a busy partition, the result will be invalid data. The ID and Query data are located at

different locations in the address map.

1st and 2nd cycles of "2 cycles write commands" must be given to the same partition address, or unexpected results will

occur.

To protect memory contents against erroneous command sequences, there are specific instances in a multi-cycle

command sequence in which the second cycle will be ignored. For example, when the device is program suspended and

an erase setup command (0x20) is given followed by a confirm/resume command (0xD0), the second command will be

ignored because it is unclear whether the user intends to erase the block or resume the program operation.

Datasheet

Intel StrataFlash® Embedded Memory (P30)

Order Number: 306666, Revision: 001

April 2005

83

INTEL [ INTEL ]

INTEL [ INTEL ]