System Bus Signal Quality Specifications

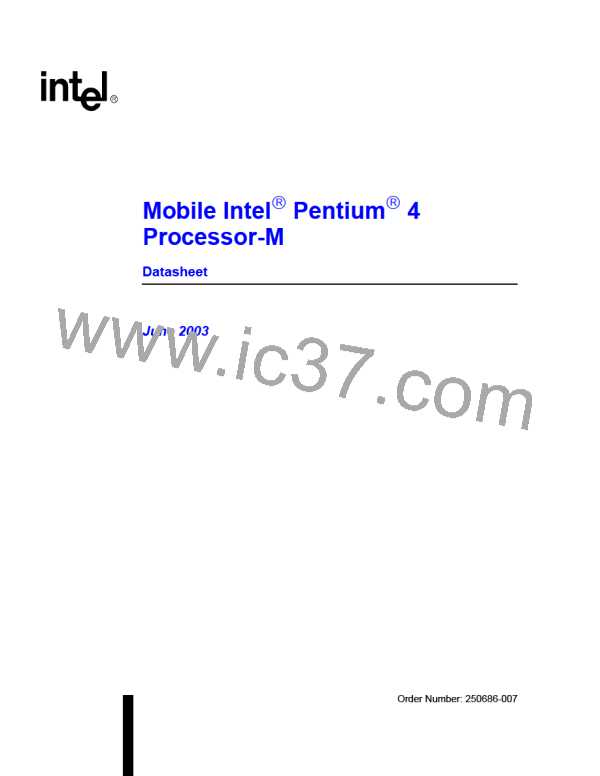

Figure 25. BCLK Signal Integrity Waveform

Overshoot

VH

BCLK1

Rising Edge

Ringback

Crossing

Voltage

Crossing

Voltage

Ringback

Margin

Threshold

Region

Falling Edge

Ringback,

BCLK0

VL

Undershoot

3.2

System Bus Signal Quality Specifications and

Measurement Guidelines

Various scenarios have been simulated to generate a set of AGTL+ layout guidelines which are

available in the Mobile Intel Pentium 4 Processor-M and Intel 845MP/845MZ Chipset

Platform Design Guide.

Table 28 and Table 29 provides the signal quality specifications for all processor signals for use in

simulating signal quality at the processor core silicon (pads).

Mobile Intel Pentium 4 Processor-M maximum allowable overshoot and undershoot specifications

for a given duration of time are detailed in Table 30 through Table 33. Figure 26 shows the system

bus ringback tolerance for low-to-high transitions and Figure 27 shows ringback tolerance for

high-to-low transitions.

Table 28. Ringback Specifications for AGTL+ and Asynchronous GTL+ Signal Groups

Maximum Ringback

(with Input Diodes Present)

Notes

Signal Group

All Signals

Transition

Unit

Figure

0 →

1 →

1

0

GTLREF + 10%

GTLREF - 10%

V

V

26

27

1,2,3,4,5,6,7

1,2,3,4,5,6,7

All Signals

NOTES:

1. All signal integrity specifications are measured at the processor silicon (pads).

2. Unless otherwise noted, all specifications in this table apply to all Mobile Intel Pentium 4 Processor-M

frequencies.

3. Specifications are for the edge rate of 0.3 - 4.0 V/ns.

4. All values specified by design characterization.

5. Please see Section 3.3 for maximum allowable overshoot.

6. Ringback between GTLREF + 10% and GTLREF - 10% is not supported.

7. Intel recommends simulations not exceed a ringback value of GTLREF +/- 200 mV to allow margin for other

sources of system noise.

52

Mobile Intel Pentium 4 Processor-M Datasheet

INTEL [ INTEL ]

INTEL [ INTEL ]