TLE 6244X

3.9 SPI Interface

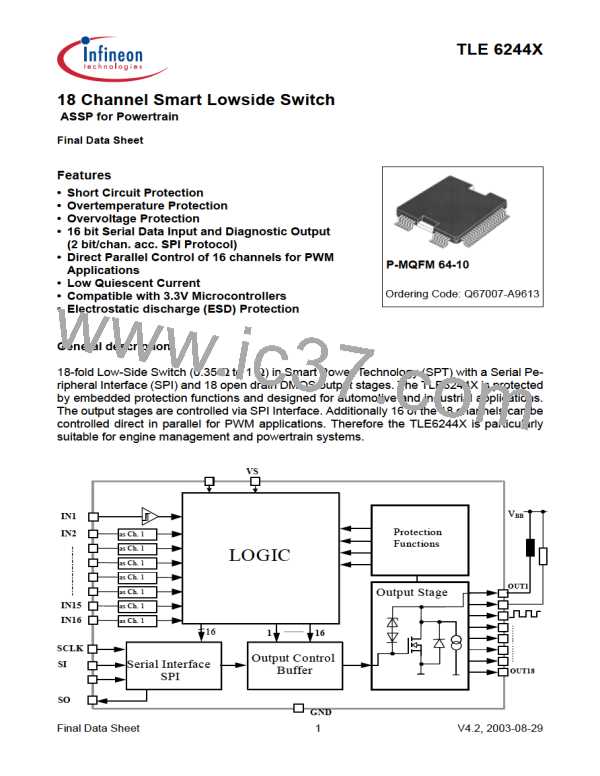

The timing of TLE6244X is defined as follows:

- The change at output (SO) is forced by the rising edge of the SCK signal.

- The input signal (SI) is sampled on the falling edge of the SCK signal.

- The data received during a writing access is taken over into the internal registers on the rising edge of the

SS

signal, if exactly 16 SPI clocks have been counted during SS = active.

(Also: Only if exactly 16 SPI clocks have been counted the instruction DEL_DIA resets the diagnostic regis-

ters.)

10

11

9

SS

3

8

2

1

SCK

14

13

12

4

7

tristate

SO

Bit (n-3)

Bit (n-4)...1

Bit 0; LSB

6

5

MSB IN

Bit (n-4)...1

LSB IN

Bit (n-2) Bit (n-3)

SI

X see 3.9.5

n = 16

Final Data Sheet

58

V4.2, 2003-08-29

INFINEON [ Infineon ]

INFINEON [ Infineon ]