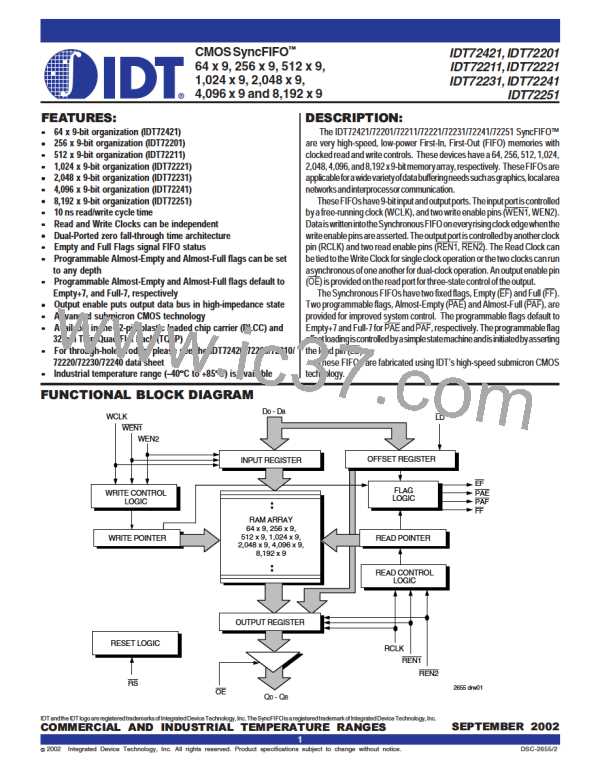

IDT72421/72201/72211/72221/72231/72241/72251 CMOS SyncFIFO™

64 x 9, 256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9 and 8,192 x 9

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

configuration,theWriteEnable2/Load(WEN2/LD)pinissetLOWatResetso

thatthepinoperatesasacontroltoloadandreadtheprogrammableflagoffsets.

OPERATINGCONFIGURATIONS

SINGLE DEVICE CONFIGURATION

AsingleIDT72421/72201/72211/72221/72231/72241/72251maybeused

when the application requirements are for 64/256/512/1,024/2,048/4,096/

8,192wordsorless.WhentheseFIFOsareinaSingleDeviceConfiguration,

theReadEnable2(REN2)controlinputcanbegrounded(seeFigure14). In

thisconfiguration,theWriteEnable2/Load(WEN2/LD)pinissetLOWatReset

sothatthe pinoperates as a controltoloadandreadthe programmable flag

offsets.

DEPTH EXPANSION - The IDT72421/72201/72211/72221/72231/72241/

72251canbeadaptedtoapplicationswhentherequirementsareforgreater

than 64/256/512/1,024/2,048/4,096/8,192 words. The existence of two

enable pins on the read and write port allow depth expansion. The Write

Enable 2/Load pin is used as a second write enable in a depth expansion

configurationthustheProgrammableflagsaresettothedefaultvalues. Depth

expansionis possiblebyusingoneenableinputforsystemcontrolwhilethe

otherenableinputiscontrolledbyexpansionlogictodirecttheflowofdata. A

typicalapplicationwouldhavetheexpansionlogicalternatedataaccessfrom

onedevicetothenextinasequentialmanner. Thesedevices operateinthe

DepthExpansionconfigurationwhenthefollowingconditionsaremet:

1. The WEN2/ LD pin is held HIGH during Reset so that this pin operates a

secondWriteEnable.

WIDTH EXPANSION CONFIGURATION

Wordwidthmaybeincreasedsimplybyconnectingthecorrespondinginput

controlssignalsofmultipledevices. Acompositeflagshouldbecreatedforeach

oftheendpointstatusflags(EFandFF). Thepartialstatusflags(AEandAF)

canbedetectedfromanyonedevice. Figure15demonstratesa18-bitword

width by using two IDT72421/72201/72211/72221/72231/72241/72251s.

AnywordwidthcanbeattainedbyaddingadditionalIDT72421/72201/72211/

72221/72231/72241/72251s.

2. Externallogicis usedtocontrolthe flowofdata.

Please see the Application Note "DEPTH EXPANSION OF IDT'S SYN-

CHRONOUSFIFOsUSINGTHERINGCOUNTERAPPROACH"fordetails

ofthisconfiguration.

When these FIFOs are in a Width Expansion Configuration, the Read

Enable 2 (REN2) control input can be grounded (see Figure 15). In this

RESET (RS)

WRITE CLOCK (WCLK)

WRITE ENABLE 1 (WEN1)

READ CLOCK (RCLK)

IDT

READ ENABLE 1 (REN1)

OUTPUT ENABLE (OE)

72421

72201

72211

72221

72231

72241

72251

WRITE ENABLE 2/LOAD (WEN2/LD)

DATA IN (D

0

- D8)

DATA OUT (Q

EMPTY FLAG (EF)

PROGRAMMABLE ALMOST-EMPTY (PAE)

0 - Q8)

FULL FLAG (FF)

PROGRAMMABLE ALMOST-FULL (PAF)

2655 drw 16

READ ENABLE 2 (REN2)

Figure 14. Block Diagram of Single 64 x 9, 256 x 9, 512 x 9, 1,024 x 9, 2,048 x 9, 4,096 x 9, 8,192 x 9 Synchronous FIFO

RESET (RS)

RESET (RS)

DATA IN (D)

18

9

9

READ CLOCK (RCLK)

WRITE CLOCK (WCLK)

READ ENABLE (REN)

OUTPUT ENABLE (OE)

PROGRAMMABLE (PAE)

WRITE ENABLE1 (WEN1)

IDT

IDT

72421

72201

72211

72221

72231

72241

72251

72421

72201

72211

72221

72231

72241

72251

WRITE ENABLE2/LOAD (WEN2/LD)

FULL FLAG (FF) #1

FULL FLAG (FF) #2

EMPTY FLAG (EF) #1

EMPTY FLAG (EF) #2

9

PROGRAMMABLE (PAF)

18

9

DATA OUT (Q)

2655 drw 17

READ ENABLE 2 (REN2)

READ ENABLE 2 (REN2)

Figure 15. Block Diagram of 64 x 18, 256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18, 4,096 x 18, 8,192 x 18

Synchronous FIFO Used in a Width Expansion Configuration

13

IDT [ INTEGRATED DEVICE TECHNOLOGY ]

IDT [ INTEGRATED DEVICE TECHNOLOGY ]