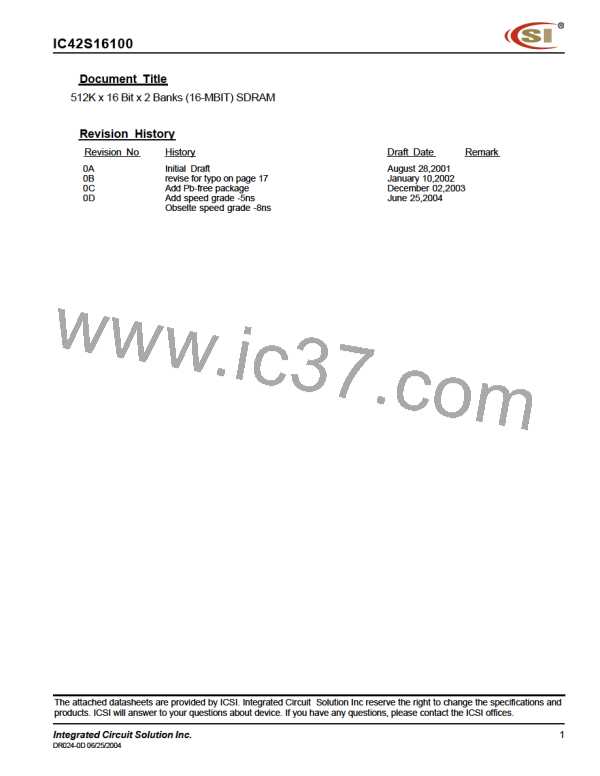

IC42S16100

Bank Active Command Interval

that bank within the ACT to PRE command period (tRAS

max). Also note that a precharge command cannot be

executed for an active bank before tRAS (min) has elapsed.

After a bank active command has been executed and the

trcd period has elapsed, read write (including auto-

precharge) commands can be executed for that bank.

When the selected bank is precharged, the period trp has

elapsed and the bank has entered the idle state, the bank

can be activated by executing the active command. If the

other bank is in the idle state at that time, the active

command can be executed for that bank after the period

tRRD has elapsed. At that point both banks will be in the

active state. When a bank active command has been

executed, a precharge command must be executed for

CLK

t

RRD

COMMAND

ACT 0

ACT 1

BANK ACTIVE (BANK 0)

BANK ACTIVE (BANK 1)

CLK

t

RCD

COMMAND

ACT 0

READ 0

BANK ACTIVE (BANK 0)

BANK ACTIVE (BANK 0)

CAS latency = 3

Clock Suspend

When the CKE pin is dropped from HIGH to LOW during a

read or write cycle, the IC42S16100 enters clock suspend

mode on the next CLK rising edge. This command reduces

the device power dissipation by stopping the device internal

clock. Clock suspend mode continues as long as the CKE

pin remains low. In this state, all inputs other than CKE pin

are invalid and no other commands can be executed. Also,

the device internal states are maintained. When the CKE

pin goes from LOW to HIGH clock suspend mode is

terminatedonthenextCLKrisingedgeanddeviceoperation

resumes.

The next command cannot be executed until the recovery

period (tCKA) has elapsed.

Since this command differs from the self-refresh command

described previously in that the refresh operation is not

performed automatically internally, the refresh operation

must be performed within the refresh period (tref). Thus the

maximum time that clock suspend mode can be held is just

under the refresh cycle time.

CLK

CKE

COMMAND

I/O

READ 0

DOUT 0

DOUT 1

DOUT 2

DOUT 3

READ (BANK 0)

CLOCK SUSPEND

CAS latency = 2, burst length = 4

Integrated Circuit Solution Inc.

35

DR024-0D 06/25/2004

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]