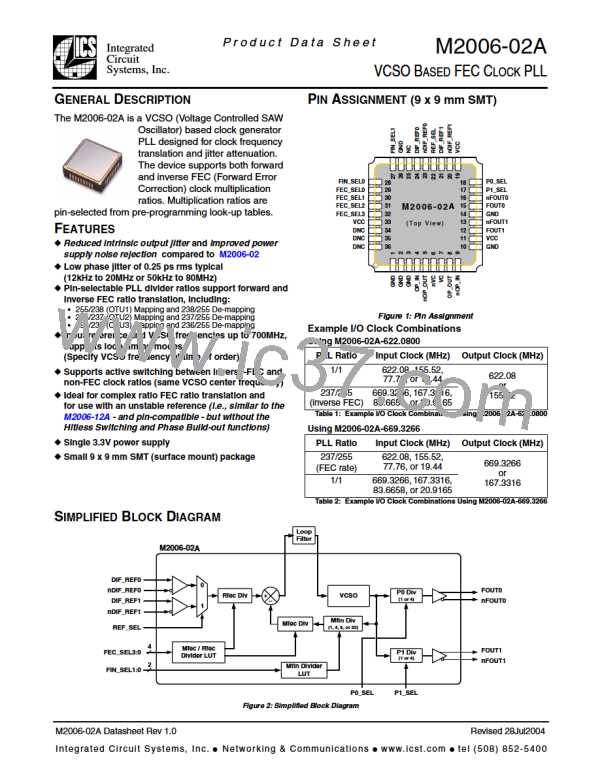

M2006-02A

Integrated

Circuit

Systems, Inc.

VCSO BASED FEC CLOCK PLL

P r o d u c t D a t a S h e e t

ELECTRICAL SPECIFICATIONS

AC Characteristics

(CONTINUED)

Unless stated otherwise, VCC

= 3.3V +5 = 622-675MHz,

%,TA = 0 oC to +70 oC (commercial), TA = -40 oC to +85 oC (industrial), FVCSO = FOUT

LVPECL outputs terminated with 50Ω to VCC - 2V

Symbol Parameter

Min

Typ

Max

Unit Test Conditions

Input

Frequency

Range

FIN

Input Frequency

DIF_REF0, nDIF_REF0,

DIF_REF1, nDIF_REF1

10

700

MHz

FOUT0, nFOUT0,

FOUT1, nFOUT1

Output

Frequency

FFOUT

APR

Output Frequency

Range

100

700

MHz

Commercial

Industrial

±120

±50

±200

±150

800

ppm

VCSO Pull-Range

ppm

KVCO

RIN

VCO Gain

kHz/V

PLL Loop

Constants

50

Internal Loop Resistor

kΩ

1

700

BWVCSO VCSO Bandwidth

kHz

Φn

Single Side Band

Phase Noise

1kHz Offset

10kHz Offset

-73

dBc/Hz

Fin=19.44 MHz

-103

-126

0.25

0.25

dBc/Hz

Mfin=32, Mfec=1, Rfec=1

PhaseNoise

and Jitter

@622.08MHz

100kHz Offset

12kHz to 20MHz

50kHz to 80MHz

P0, P1 = 1

dBc/Hz

ps rms

ps rms

%

0.5

0.5

60

J(t)

tPW

Jitter (rms)

@622.08MHz

2

Output Duty Cycle

FOUT0, nFOUT0,

40

50

45

50

55

P0, P1 = 4

%

FOUT1, nFOUT

1

2

200

200

450

450

500

500

tR

tF

Output Rise Time

ps

ps

20% to 80%

20% to 80%

FOUT0, nFOUT0,

FOUT1, nFOUT1

2

Output Fall Time

Table 12: AC Characteristics

Note 1: Parameters needed for PLL Simulator software; see Table 8, Example External Loop Filter Component Values, on pg. 5.

Note 2: See Parameter Measurement Information on pg. 7.

PARAMETER MEASUREMENT INFORMATION

Output Rise and Fall Time

Output Duty Cycle

nFOUT

FOUT

80%

80%

VP-P

tPW

(Output Pulse Width)

20%

t

F

20%

Clock Output

t

R

tPERIOD

t

PW

odc =

t

PERIOD

Figure 6: Output Duty Cycle

Figure 5: Output Rise and Fall Time

M2006-02A Datasheet Rev 1.0

7 of 8

Revised 28Jul2004

Integrated Circuit Systems, Inc. ● Networking & Communications ● www.icst.com ● tel (508) 852-5400

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]