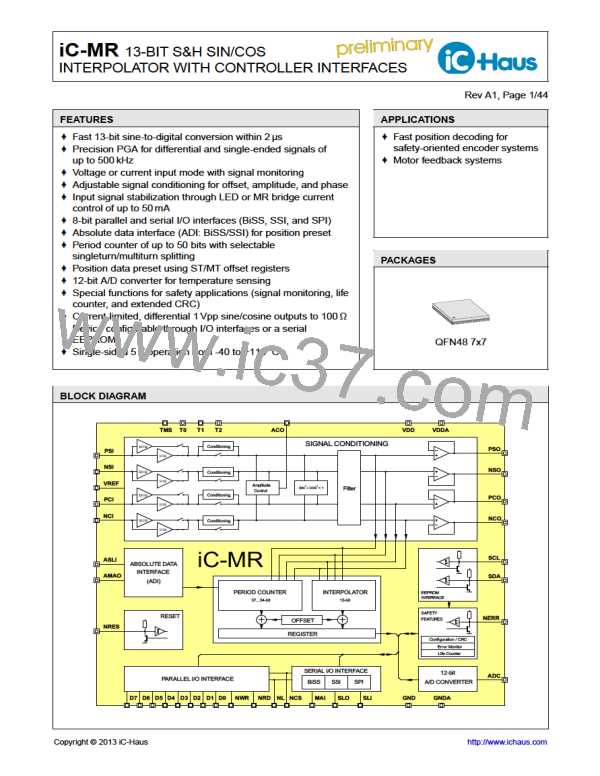

iC-MR 13-BIT S&H SIN/COS

INTERPOLATOR WITH CONTROLLER INTERFACES

Rev A1, Page 9/44

ELECTRICAL CHARACTERISTICS

Operating conditions:

VDDA = VDD = 4.5...5.5 V, GNDA = GND = 0 V, IBP calibrated to 200 µA, Tj = -40...125 °C, unless otherwise noted.

Item Symbol

No.

Parameter

Conditions

Unit

Min.

Typ.

Max.

13-bit Interpolator

C01 tipo

Conversion Time

ACQMODE = 00, see Figure 5

Vpk() = 250 mV

2

2

µs

C02 AAabs

Absolute Conversion Accuracy

LSB

Reset Input / Reset Indication Output NRES

K01 VDDon

K02 VDDoff

K03 VDDhys

K04 Vt()hi

K05 Vt()lo

K06 Vt()hys

K07 Ipu()

VDD Turn-on Threshold

VDD Turn-off Threshold

VDD Hysteresis

increasing voltage at VDD vs. GND

decreasing voltage at VDD vs. GND

VDDhys = VDDon - VDDoff

2.6

2.3

400

4.3

4.0

V

V

mV

V

Input Threshold Voltage hi

Input Threshold Voltage lo

Input Hysteresis

2

0.8

300

-750

V

Vt()hys = Vt()hi - Vt()lo

500

mV

µA

mV

mA

Pull-up Current

-300

-60

400

80

K08 Vs()lo

K09 Isc()lo

Oscillator

Output Saturation Voltage lo

Output Short-Circuit Current lo

I() = 4 mA

V() = 0.4 V...VDD

4

M01 fosc

Internal Oscillator Frequency

15

MHz

EEPROM Interface SCL, SDA

N01 Vs()lo

N02 Isc()

N03 Vt()hi

N04 Vt()lo

N05 Vt()hys

N06 Ipu()

N07 Vpu()

N08 fclk()

Saturation voltage lo

I() = 4 mA

400

80

2

mV

mA

V

Short-Circuit Current lo

Input Threshold Voltage hi

Input Threshold Voltage lo

Input Hysteresis

4

0.8

100

-750

V

Vt()hys = Vt()hi - Vt()lo

V() = 0 V...VDD - 1 V

250

mV

µA

V

Input Pull-up Current

-300

-60

0.4

Input Pull-up Voltage

Vpu() = VDD - V(), I() = -5 µA

Clock Frequency at SCL

100

120

130

kHz

N09

tbusy()cfg Duration of Configuration Phase

IBP not adjusted;

read in of EEPROM

no EEPROM connected

5

1

ms

ms

Serial Interface MAI, SLO, SLI

O01 Vt()hi

O02 Vt()lo

O03 Vt()Hys

O04 Ipu()

O05 Ipd()

Threshold Voltage hi at SLI, MAI

2

V

V

Threshold Voltage lo at SLI, MAI

Hysteresis at SLI, MAI

0.8

300

-150

8

Vt()hys = Vt()hi - Vt()lo

500

-60

60

mV

µA

µA

Pull-up Current at MAI

-8

Pull-down Current at SLI

150

O06

fclk()

Permissible Clock Frequency at

MAI

SSI protocol

BiSS C protocol

SPI

4

10

10

MHz

MHz

MHz

O07 tp()

Propagation Delay at SLO versus

Clock Edge MAI

10

50

ns

O08 tbusy()

Processing Time

Adaptive Timeout

ACQMODE = 00, see Figure 5

t()ipo

O09

ttimeout

1/fosc

1.5*tMAS

+

3/fosc

O10 Vs()hi

O11 Vs()lo

O12 Isc()hi

O13 Isc()lo

Saturation Voltage hi at SLO

Saturation Voltage lo at SLO

Short-circuit Current hi at SLO

Short-circuit Current lo at SLO

Vs()hi = VDD - V(), I() = -4 mA

I() = 4 mA

400

400

-4

mV

mV

mA

mA

V() = 0 V...VDD - 0.4 V

V() = 0.4 V...VDD

-80

4

80

Parallel Interface D(7...0), NWR, NRD, NL, NCS

P01 Vt()hi

P02 Vt()lo

P03 Vt()hys

P04 Ipu()

Threshold Voltage hi

Threshold Voltage lo

Input Hysteresis

D(7...0) as input

2

V

V

D(7...0) as input

0.8

300

-70

D(7...0) as input, Vt()hys = Vt()hi - Vt()lo

500

-30

mV

µA

Pull-up Current at D(7...0)

-5

ICHAUS [ IC-HAUS GMBH ]

ICHAUS [ IC-HAUS GMBH ]