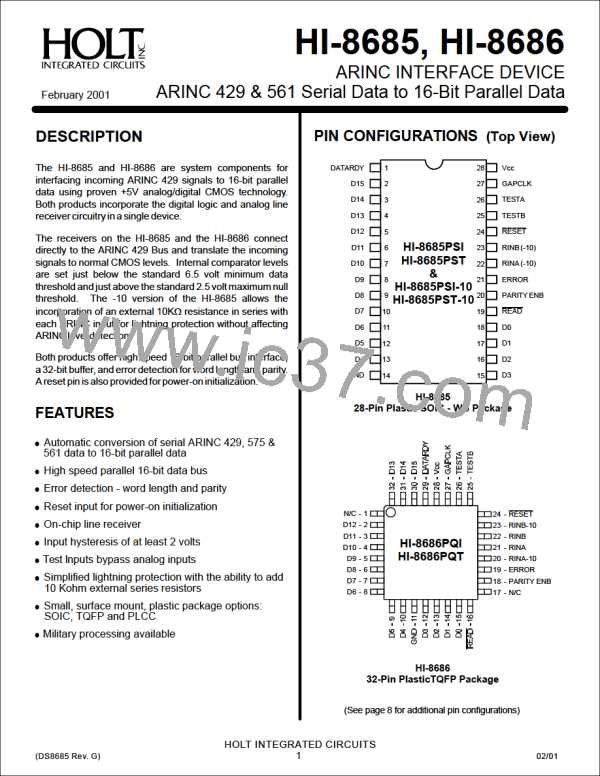

| 型号: | HI-8686PQI |

| PDF下载: | 下载PDF文件 查看货源 |

| 内容描述: | ARINC接口设备ARINC 429 & 561串行数据转换为16位并行数据 [ARINC INTERFACE DEVICE ARINC 429& 561 SERIAL DATA TO 16-BIT PARALLEL DATA] |

| 分类和应用: | |

| 文件页数/大小: | 10 页 / 242 K |

| 品牌: |  HOLTIC [ HOLT INTEGRATED CIRCUITS ] HOLTIC [ HOLT INTEGRATED CIRCUITS ] |

专业IC领域供求交易平台:提供全面的IC Datasheet资料和资讯,Datasheet 1000万数据,IC品牌1000多家。