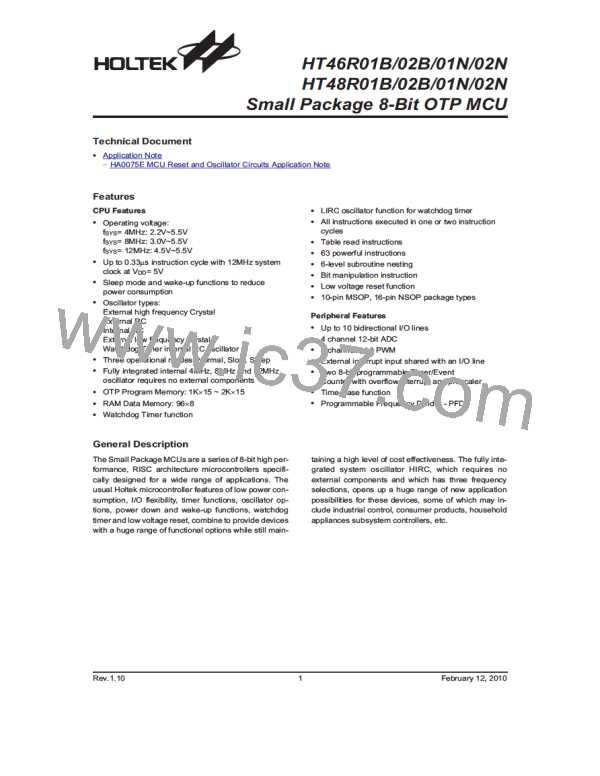

HT46R01B/02B/01N/02N

HT48R01B/02B/01N/02N

The following table indicates the way in which the various components of the microcontroller are affected after a

power-on reset occurs.

Item

Program Counter

Interrupts

Condition After RESET

Reset to zero

All interrupts will be disabled

WDT

Clear after reset, WDT begins counting

Timer/Event Counter Timer Counter will be turned off

Prescaler

The Timer Counter Prescaler will be cleared

Input/Output Ports

Stack Pointer

I/O ports will be setup as inputs

Stack Pointer will point to the top of the stack

The different kinds of resets all affect the internal registers of the microcontroller in different ways. To ensure reliable

continuation of normal program execution after a reset occurs, it is important to know what condition the microcontroller

is in after a particular reset occurs. The following table describes how each type of reset affects each of the

microcontroller internal registers.

HT46R01B/HT46R02B/HT46R01N/HT46R02N

Power-on

Reset

RES or LVR

Reset

WDT Time-out

WDT Time-out

(Sleep)

Register

(Normal Operation)

PCL

MP0

MP1

ACC

0 0 0 0 0 0 0 0

x x x x x x x x

x x x x x x x x

x x x x x x x x

x x x x x x x x

- x x x x x x x

- - - - - 1 1 1

- - 0 0 x x x x

- 0 0 0 0 0 0 0

- - 0 0 - - 0 0

x x x x x x x x

0 0 0 0 1 0 0 0

x x x x x x x x

0 0 0 0 1 - - -

1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1

0 0 0 0 0 0 0 0

- 0 0 0 0 0 0 0

- - - - - - 1 1

- - - - - - 1 1

- - - - - - 0 0

- 0 0 - 0 0 0 0

1 0 0 0 1 0 1 0

x x x x x x x x

0 0 0 0 0 0 0 0

u u u u u u u u

u u u u u u u u

u u u u u u u u

u u u u u u u u

- u u u u u u u

- - - - - 1 1 1

- - u u u u u u

- 0 0 0 0 0 0 0

- - 0 0 - - 0 0

x x x x x x x x

0 0 0 0 1 0 0 0

x x x x x x x x

0 0 0 0 1 - - -

1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1

0 0 0 0 0 0 0 0

- 0 0 0 0 0 0 0

- - - - - - 1 1

- - - - - - 1 1

- - - - - - 0 0

- 0 0 - 0 0 0 0

1 0 0 0 1 0 1 0

x x x x x x x x

0 0 0 0 0 0 0 0

u u u u u u u u

u u u u u u u u

u u u u u u u u

u u u u u u u u

- u u u u u u u

- - - - - 1 1 1

- - 1 u u u u u

- 0 0 0 0 0 0 0

- - 0 0 - - 0 0

x x x x x x x x

0 0 0 0 1 0 0 0

x x x x x x x x

0 0 0 0 1 - - -

1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1

0 0 0 0 0 0 0 0

- 0 0 0 0 0 0 0

- - - - - - 1 1

- - - - - - 1 1

- - - - - - 0 0

- 0 0 - 0 0 0 0

1 0 0 0 1 0 1 0

x x x x x x x x

0 0 0 0 0 0 0 0

u u u u u u u u

u u u u u u u u

u u u u u u u u

u u u u u u u u

- u u u u u u u

- - - - - u u u

- - 1 1 u u u u

- u u u u u u u

- - u u - - u u

u u u u u u u u

u u u u u u u u

u u u u u u u u

u u u u u - - -

u u u u u u u u

u u u u u u u u

u u u u u u u u

- u u u u u u u

- - - - - - u u

- - - - - - u u

- - - - - - u u

- u u - u u u u

u u u u u u u u

u u u u u u u u

TBLP

TBLH

WDTS

STATUS

INTC0

INTC1

TMR0

TMR0C

TMR1

TMR1C

PA

PAC

PAWK

PAPU

PB

PBC

PBPU

CTRL0

CTRL1

PWM0

Rev.1.10

27

February 12, 2010

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]