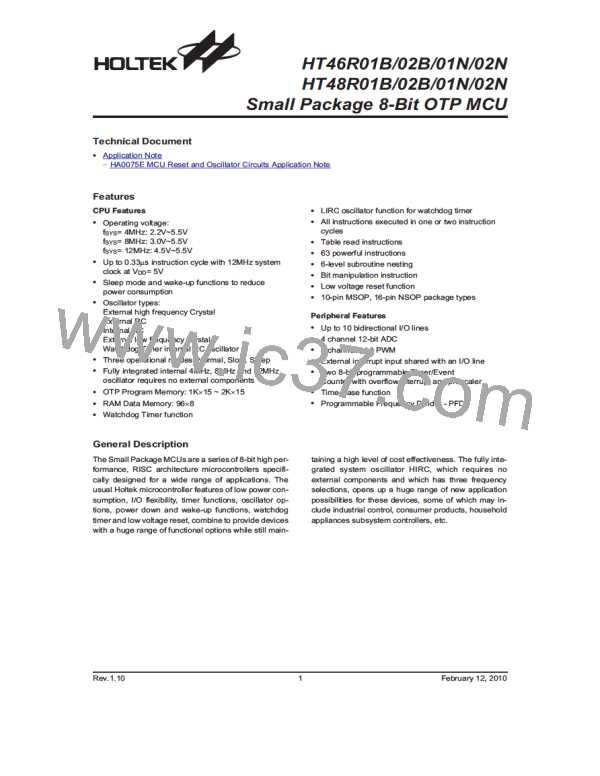

HT46R01B/02B/01N/02N

HT48R01B/02B/01N/02N

Operating Modes

By using the LXT low frequency oscillator in combina-

tion with a high frequency oscillator, the system can be

selected to operate in a number of different modes.

These Modes are Normal, Slow and Sleep.

OSC1/OSC2 Configuration

Operating

Mode

HIRC + LXT

ERC HIRC

HXT

HIRC

LXT

Run

Run

Run

Mode Types and Selection

Normal

Slow

Run

¾

Run

¾

Run

¾

Run

The higher frequency oscillators provide higher perfor-

mance but carry with it the disadvantage of higher

power requirements, while the opposite is of course true

for the lower frequency oscillators. With the capability of

dynamically switching between fast and slow oscillators,

the device has the flexibility to optimise the perfor-

mance/power ratio, a feature especially important in

power sensitive portable applications.

Stop

Stop

Sleep

Stop

Stop

Stop

²¾² unimplemented

Operating Mode Control

Mode Switching

The devices are switched between one mode and an-

other using a combination of the CLKMOD bit in the

CTRL0 register and the HALT instruction. The CLKMOD

bit chooses whether the system runs in either the Nor-

mal or Slow Mode by selecting the system clock to be

sourced from either a high or low frequency oscillator.

The HALT instruction forces the system into either the

Sleep Mode, depending upon whether the LXT oscilla-

tor is running or not. The HALT instruction operates in-

dependently of the CLKMOD bit condition.

If the LXT oscillator is used then the internal RC oscilla-

tor, HIRC, must be used as the high frequency oscillator.

If the HXT or the ERC oscillator is chosen as the high

frequency system clock then the LXT oscillator cannot

be used for sharing the same pins. The CLKMOD bit in

the CTRL0 register can be used to switch the system

clock from the high speed HIRC oscillator to the low

speed LXT oscillator. When the HALT instruction is exe-

cuted and the device enters the Sleep Mode the LXT os-

cillator will always continue to run. For the device the

LXT crystal is connected to the OSC1/OSC2 pins and

LXT will always run.

When a HALT instruction is executed and the LXT oscil-

lator is not running, the system enters the Sleep mode

the following conditions exist:

Note that CLKMOD is only valid in HIRC+LXT oscillator

configuration.

·

·

·

The system oscillator will stop running and the appli-

cation program will stop at the ²HALT² instruction.

The Data Memory contents and registers will maintain

their present condition.

When the system enters the Sleep Mode, the high fre-

quency system clock will always stop running. The ac-

companying tables shows the relationship between the

CLKMOD bit, the HALT instruction and the high/low fre-

quency oscillators. The CLMOD bit can change normal

or Slow Mode.

The WDT will be cleared and resume counting if the

WDT clock source is selected to come from the WDT

or LXT oscillator. The WDT will stop if its clock source

originates from the system clock.

f

H

X

T

C

L

K

M

O

D

H

X

T

(

D

e

t

e

r

m

i

n

e

N

o

r

m

a

C

o

n

f

i

g

u

r

a

t

i

o

n

o

p

t

i

o

n

d

S

l

o

w

M

o

e

)

f

E

R

C

E

R

C

(

N

o

r

m

a

l

)

M

U

X

M

U

X

f

S

Y

S

f

H

I

R

C

H

I

R

C

(

S

L

O

W

)

f

L

X

T

L

X

T

C

o

n

f

i

g

u

r

a

t

i

o

n

o

p

t

i

o

n

f

L

I

R

C

M

U

X

L

I

R

C

T

o

w

a

t

c

h

d

o

g

t

i

m

e

r

f

S

Y

S

System Clock Configurations

Rev.1.10

22

February 12, 2010

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]