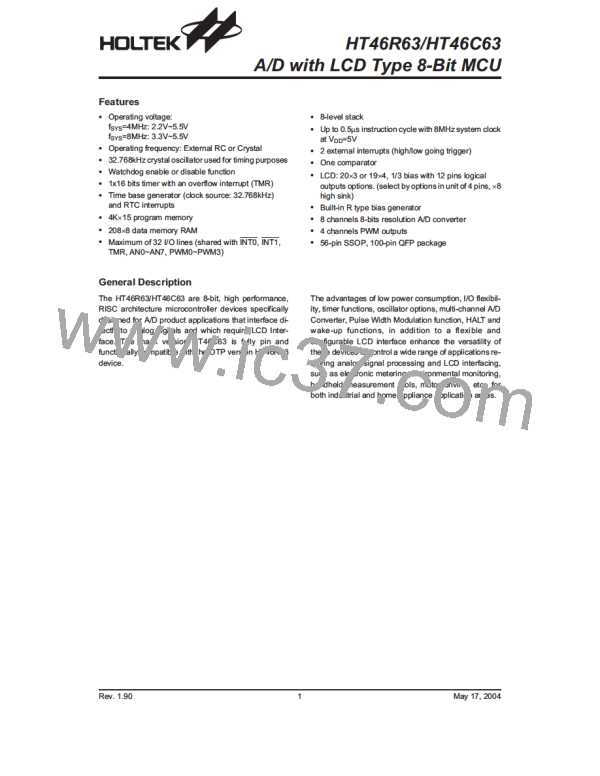

HT46R63/HT46C63

Label (ADCR)

Bits

Functions

ACS2, ACS1, ACS0: A/D channel selection

0,0,0: AN0

0,0,1: AN1

0,1,0: AN2

0,1,1: AN3

1,0,0: AN4

1,0,1: AN5

1,1,0: AN6

1,1,1: AN7

ACS0

ACS1

ACS2

0

1

2

PCR2, PCR1, PCR0: PB7~PB0 pad functions

0,0,0: PB7, PB6, PB5, PB4, PB3, PB2, PB1, PB0

0,0,1: PB7, PB6, PB5, PB4, PB3, PB2, PB1, AN0

0,1,0: PB7, PB6, PB5, PB4, PB3, PB2, AN1, AN0

0,1,1: PB7, PB6, PB5, PB4, PB3, AN2, AN1, AN0

1,0,0: PB7, PB6, PB5, PB4, AN3, AN2, AN1, AN0

1,0,1: PB7, PB6, PB5, AN4, AN3, AN2, AN1, AN0

1,1,0: PB7, PB6, AN5, AN4, AN3, AN2, AN1, AN0

1,1,1: AN7, AN6, AN5, AN4, AN3, AN2, AN1, AN0

PCR0

PCR1

PCR2

3

4

5

End of A/D conversion flag

(0: end of A/D conversion)

EOCB

START

Note:

6

7

A/D conversion sequence (START=010)

0: Initial value after chip RESET

0®1: Initial next A/D conversion.

1: reset A/D converter and set EOCB to ²1²

1®0: Starts the A/D conversion.

0: Normal state for A/D

It is recommended that START is ²0² and PCR2~PCR0 is ²000² before MCU entering HALT mode.

HALT will not standby the A/D converter automatically.

ACSR Register

Label (ACSR)

Bits

Functions

ADCS1, ADCS0: Selects the A/D converter clock source

0,0: fSYS/2

ADCS0

ADCS1

0

1

0,1: fSYS/8

1,0: fSYS/32

1,1: Cannot be used

Comparator control (*)

0: Disable

CMPC

¾

2

3~6

7

1: Enable

Unused bit, read as ²0²

For test mode used only

0: Normal mode

TEST

1: TEST only, cannot be used

Note:

²*² This bit is 0 during reset.

Rev. 1.90

22

May 17, 2004

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]