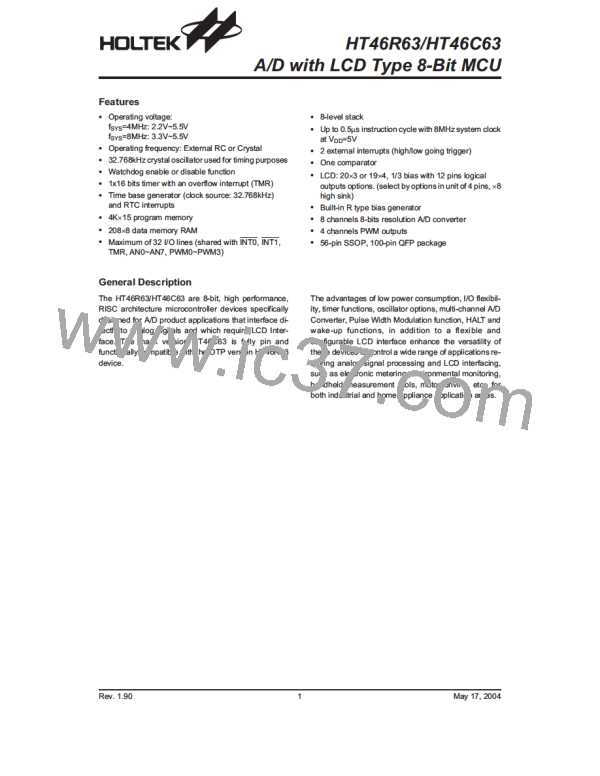

HT46R63/HT46C63

M

i

n

i

m

u

m

o

n

e

i

n

s

t

r

u

c

t

i

o

n

c

y

c

l

e

n

e

e

d

e

d

S

T

A

R

T

E

O

C

B

A

/

D

s

a

m

p

l

i

n

g

t

i

m

e

A

/

D

s

a

m

p

l

i

n

g

t

i

m

e

3

2

t

A

D

3

2

t

P

C

R

2

~

P

C

R

0

0

0

0

B

1

0

0

B

0

0

0

B

1

0

0

B

1

.

P

A

t

B

p

o

r

t

s

e

t

u

p

a

s

I

/

O

s

2

.

/

D

c

o

n

v

e

r

t

e

r

i

s

p

o

w

e

r

e

d

o

f

f

o

r

e

d

u

c

e

p

o

w

e

r

c

o

n

s

u

m

p

t

i

o

n

d

o

n

'

t

c

a

r

e

A

C

S

2

~

A

C

S

0

0

0

0

B

0

0

0

B

0

1

0

B

P

o

w

e

r

-

o

n

S

t

a

r

t

o

f

A

/

D

S

t

a

r

t

o

f

A

/

D

R

e

s

e

t

c

o

n

v

e

r

s

i

o

n

c

o

n

v

e

r

s

i

o

n

R

e

s

e

t

A

/

D

R

e

s

e

t

A

/

D

c

o

n

v

e

r

t

e

r

c

o

n

v

e

r

t

e

r

E

n

d

o

f

A

/

D

E

n

d

o

f

A

/

D

c

o

n

v

e

r

s

i

o

n

c

o

n

v

e

r

s

i

o

n

1

:

D

e

f

i

n

e

P

B

c

o

n

f

i

g

u

r

a

t

i

o

n

2

:

S

e

l

e

c

t

a

n

a

l

o

g

c

h

a

n

n

e

l

6

4

t

A

D

6

4

t

A

/

D

c

o

n

v

e

r

s

i

o

n

t

i

m

e

A

/

D

c

o

n

v

e

r

s

i

o

n

t

i

m

e

N

o

t

e

:

S

Y

S

S

Y

S

S

Y

S

A/D Conversion Timing

PWM

and the output function of PDi is enabled, writing ²1² to

PDi data register will enable the PWMi output function.

Otherwise the PDi will stay at ²0². The PWM modulation

frequency, PWM cycle frequency and PWM cycle duty

are summarized in the following table.

The micro-controller provides 4 channels (6+2) bits

PWM outputs shared with PD0~PD3. The PWM chan-

nels has their data register. The PWMs uses a PWM

counter whose stages are 8 (stage 1~stage 8: fSYS/21 ~

f

SYS/28). The frequency source of the PWM counter co-

PWMi Modulation PWMi Cycle

PWMi Cycle

Duty

mes from fSYS. The PWM register is an eight bits regis-

ter. The waveforms of PWM outputs are as shown.

Once the PDi (i=0~3) is selected as the PWMi output

Frequency

Frequency

fSYS/64

fSYS/256

[PWM]/256

S

Y

S

[

[

[

[

P

P

P

P

W

W

W

W

M

M

M

M

]

]

]

]

=

=

=

=

1

1

1

1

0

0

0

0

0

1

2

3

P

P

P

P

W

W

W

W

M

M

M

M

2

5

/

6

4

2

2

2

2

5

5

6

6

/

/

/

/

6

6

6

6

4

4

4

4

2

2

2

2

5

5

5

6

/

/

/

/

6

6

6

6

4

4

4

4

2

2

2

2

5

5

5

5

/

/

/

/

6

6

6

6

4

4

4

4

2

2

2

2

5

6

6

6

/

/

/

/

6

6

6

6

4

4

4

4

2

2

2

6

6

6

/

/

/

6

6

6

4

4

4

P

W

M

m

o

d

u

l

a

t

i

o

n

p

e

r

i

o

d

:

6

4

/

f

M

o

d

u

l

a

t

i

o

n

c

y

c

l

e

0

M

o

d

u

l

a

t

i

o

n

c

y

c

l

e

1

M

o

d

u

l

a

t

i

o

n

c

y

c

l

e

2

M

o

d

u

l

a

t

i

o

n

c

y

c

l

e

3

M

o

d

u

l

a

t

i

o

n

c

y

c

l

e

0

P

W

M

c

y

c

l

e

:

2

5

6

/

f

PWM Mode

Rev. 1.90

24

May 17, 2004

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]