HT37B90/HT37B70/HT37B50/HT37B30

Table Location Bits

Instruction

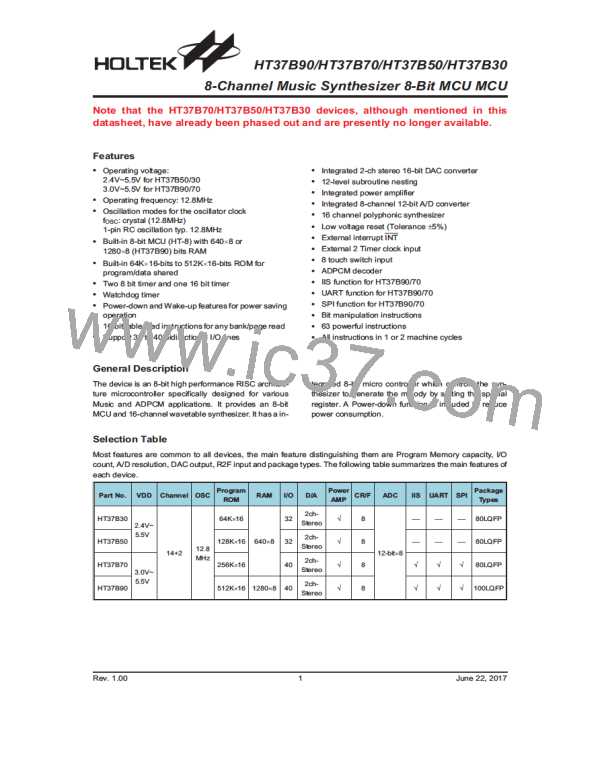

b18~b13

TABRDC [m] TBHP1_2~TBMP1_5 TBMP1_4~TBMP1_0 @7

TABRDL [m] BP1_5~BP1_0 11111 @7

b12~b8

b7

b6

@6

@6

b5

@5

@5

b4

@4

@4

b3

@3

@3

b2

@2

@2

b1

@1

@1

b0

@0

@0

Table Location

Note: @7~@0: Table pointer lower-order bits are TBLP1 [7:0]

b17~b0: Current program ROM table address A [18:0]

TBMP1_4~TBMP1_0: TBMP1 bit 4 ~0

TBHP1_2~TBMP1_5: TBHP1 (bit 2 ~0) to TBMP1 (bit7 ~5)

BP1_5 ~BP1_0: Bits of bank BP1 bit0~5

For the HT37B90, the Table address location is 19 bits wide, i.e. from b18~b0.

For the HT37B70, the Table address location is 18 bits wide, i.e. from b17~b0.

For the HT37B50, the Table address location is 17 bits wide, i.e. from b16~b0.

For the HT37B30, the Table address location is 16 bits wide, i.e. from b15~b0.

tempreg1 db

tempreg2 db

tempreg3 db

tempreg4 db

?

?

?

?

; temporary register #1

; temporary register #2

; temporary register #3

; temporary register #4

:

:

mov a,01h

; set ROM bank 1 point

mov bp1,a

mov a,06h

mov tblp1,a

clr tbmpl

clr tbhpl

; initialise table pointer

; to the last page

:

:

tabrdl

tempreg1

tempreg2

; transfers value in table referenced by table pointer

; to tempregl

; data at prog. memory address ²3F06H² transferred to

; tempreg1 and TBLH

dec tblp1

tabrdl

; reduce value of table pointer by one

; transfers value in table referenced by table pointer

; to tempreg2

; data at prog.memory address ²3F05H² transferred to

; tempreg2 and TBLH

; in this example the data ²1AH² is transferred to

; tempreg1 and data ²0FH² to register tempreg2

; the value ²00H² will be transferred to the high byte

; register TBLH

:

:

mov a,04h

mov tblp1,a

mov a,3Fh

; initialise table pointer low byte

;

; initialise table pointer middle byte

mov tbmp1,a

mov a,00h

; initialise table pointer high byte

;

mov tbhp1,a

tabrdc

tempreg3

:

:

rombank

1

romsumvalue1; sets rombank 1 initial address of last page

;(for HT37B90/70/50/30)

romsumvalue1 .section at 1F00h ¢code¢

dc 00Ah, 00Bh, 00Ch, 00Dh, 00Eh, 00Fh, 01Ah, 01Bh

:

:

Rev. 1.00

13

June 22, 2017

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]