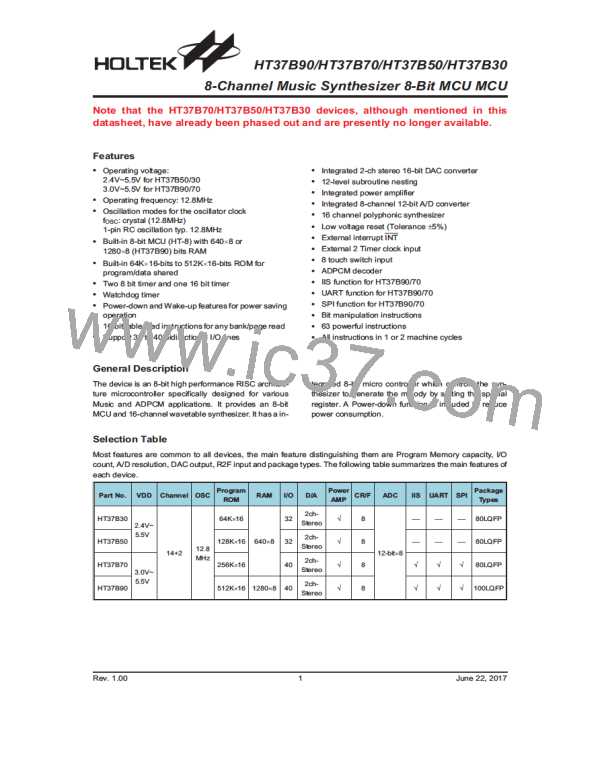

HT37B90/HT37B70/HT37B50/HT37B30

When executing instructions requiring jumps to

non-consecutive addresses such as a jump instruction,

a subroutine call, interrupt or reset, etc., the

microcontroller manages program control by loading the

required address into the Program Counter. For condi-

tional skip instructions, once the condition has been

met, the next instruction, which has already been

fetched during the present instruction execution, is dis-

carded and a dummy cycle takes its place while the cor-

rect instruction is obtained.

The lower byte of the Program Counter is fully accessi-

ble under program control. Manipulating the PCL might

cause program branching, so an extra cycle is needed

to pre-fetch. Further information on the PCL register can

be found in the Special Function Register section.

Stack

This is a special part of the memory which is used to

save the contents of the Program Counter only. The

stack can have 12 levels depending upon which option

is selected and is neither part of the data nor part of the

program space, and is neither readable nor writable.

The activated level is indexed by the Stack Pointer, SP,

and is neither readable nor writable. At a subroutine call

or interrupt acknowledge signal, the contents of the Pro-

gram Counter are pushed onto the stack. At the end of a

subroutine or an interrupt routine, signaled by a return

instruction, RET or RETI, the Program Counter is re-

stored to its previous value from the stack. After a de-

vice reset, the Stack Pointer will point to the top of the

stack.

The lower byte of the Program Counter, known as the

Program Counter Low register or PCL, is available for

program control and is a readable and writable register.

By transferring data directly into this register, a short

program jump can be executed directly, however, as

only this low byte is available for manipulation, the

jumps are limited to the present page of memory, that is

256 locations. When such program jumps are executed

it should also be noted that a dummy cycle will be in-

serted.

Program Counter

Mode

b18~b13

b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Initial Reset

000000

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

Timer/Event Counter 0

Overflow

000000

000000

000000

Timer/Event Counter 1

Overflow

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

1

0

0

0

0

0

Timer Counter 2

Overflow (UART)

ERCOCI Interrupt

ADPCM Interrupt

Skip

000000

000000

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

1

1

0

0

0

0

0

Program Counter + 2 (Within Current Bank)

P12 P11 P10 P9 P8 @7 @6 @5 @4 @3 @2 @1 @0

Loading PCL

Jump, Call Branch

P18~P13

BP1.5~BP1.0 #12 #11 #10 #9 #8 #7 #6 #5 #4 #3 #2 #1 #0

Return from Subroutine S18~S13

S12 S11 S10 S9 S8 S7 S6 S5 S4 S3 S2 S1 S0

Program Counter

Note: P18~P8: Program Counter bits

@7~@0: PCL bits

#12~#0: Instruction code address bits

BP1.5~BP1.0: ROM bank pointer

S18~S0: Stack register bits

For the HT37B90, the Program Counter is 19 bits wide, i.e. from b18~b0.

For the HT37B70, the Program Counter is 18 bits wide, i.e. from b17~b0, therefore the b18 column in the

table is not applicable.

For the HT37B50, the Program Counter is 17 bits wide, i.e. from b16~b0, therefore the b17 and b18 column in

the table is not applicable.

For the HT37B30, the Program Counter is 16 bits wide, i.e. from b15~b0, therefore the b18, b17 and b16 the

columns in the table are not applicable.

Rev. 1.00

10

June 22, 2017

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]