HT36M4

Oscillator Configuration

malfunction or sequence jumping to an unknown loca-

tion with unpredictable results. The Watchdog Timer can

be disabled by mask option. If the Watchdog Timer is

disabled, all executions related to the WDT result in no

operation.

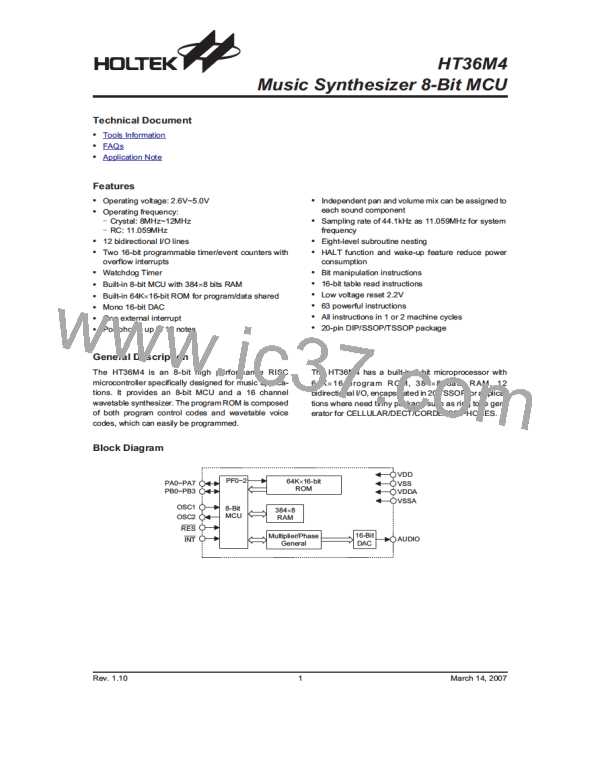

The HT36M4 provides two types of oscillator circuit for

the system clock, i.e., RC oscillator and crystal oscilla-

tor. No matter what type of oscillator, the signal divided

by 2 is used for the system clock (fSYS=fOSC/2). The

HALT mode stops the system oscillator and ignores ex-

ternal signal to conserve power. If the RC oscillator is

used, an external resistor between OSC1 and VSS is re-

quired, and the range of the resistance should be from

30kW to 680kW. The system clock, divided by 4

(fOSC2=fSYS/4=fOSC/8), is available on OSC2 with

pull-high resistor, which can be used to synchronize ex-

ternal logic. The RC oscillator provides the most cost ef-

fective solution. However, the frequency of the

oscillation may vary with VDD, temperature, and the

chip itself due to process variations. It is therefore, not

suitable for timing sensitive operations where accurate

oscillator frequency is desired.

Once the internal WDT oscillator (RC oscillator with a

period of 78ms normally) is selected, it is first divided by

256 (8-stages) to get the nominal time-out period of ap-

proximately 20ms. This time-out period may vary with

temperature, VDD and process variations. By invoking

the WDT prescaler, longer time-out periods can be real-

ized. Writing data to WS2, WS1, WS0 (bits 2, 1, 0 of the

WDTS) can give different time-out periods. If WS2,

WS1, WS0 all equal to 1, the division ratio is up to 1:128,

and the maximum time-out period is 2.6 seconds.

If the WDT oscillator is disabled, the WDT clock may still

come from the instruction clock and operate in the same

manner except that in the HALT state the WDT may stop

counting and lose its protecting purpose. In this situation

the logic can only be restarted by external logic. The

high nibble and bit 3 of the WDTS are reserved for user

defined flags, and the programmer may use these flags

to indicate some specified status.

On the other hand, if the crystal oscillator is selected, a

crystal across OSC1 and OSC2 is needed to provide the

feedback and phase shift required for the oscillator, and

no other external components are required. A resonator

may be connected between OSC1 and OSC2 to replace

the crystal and to get a frequency reference, but two ex-

ternal capacitors in OSC1 and OSC2 are required.

WS2

WS1

WS0

Division Ratio

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1:1

1:2

The WDT oscillator is a free running on-chip RC oscilla-

tor, and no external components are required. Even if

the system enters the power down mode, the system

clock is stopped, but the WDT oscillator still works with a

period of approximately 78ms. The WDT oscillator can

be disabled by mask option to conserve power.

1:4

1:8

1:16

1:32

1:64

1:128

O

S

C

1

O

S

C

1

V

D

D

If the device operates in a noisy environment, using the

on-chip RC oscillator (WDT OSC) is strongly recom-

mended, since the HALT will stop the system clock.

O

S

C

2

f

O

S

C

/

8

O

S

C

2

C

r

y

s

t

a

l

O

s

c

i

l

l

a

t

o

r

R

C

O

s

c

i

l

l

a

t

o

r

System Oscillator

The WDT overflow under normal operation will initialize

a ²chip reset² and set the status bit TO. Whereas in the

HALT mode, the overflow will initialize a ²warm reset²

only the Program Counter and Stack Pointer are reset to

zero. To clear the WDT contents (including the WDT

prescaler), three methods are implemented; external re-

set (a low level to RES), software instructions, or a HALT

Watchdog Timer - WDT

The WDT clock source is implemented by a dedicated

RC oscillator (WDT oscillator) or instruction clock (sys-

tem clock of the MCU divided by 4), determined by mask

options. This timer is designed to prevent a software

O

S

C

W

D

T

P

r

e

s

c

a

l

e

r

M

a

s

k

8

-

b

i

t

C

o

u

n

t

e

r

7

-

b

i

t

C

o

u

n

t

e

r

O

p

t

i

o

n

S

e

l

e

c

t

W

D

T

O

S

C

8

-

t

o

-

1

M

U

X

W

S

0

~

W

S

2

W

D

T

T

i

m

e

-

o

u

t

Watchdog Timer

Rev. 1.10

10

March 14, 2007

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]