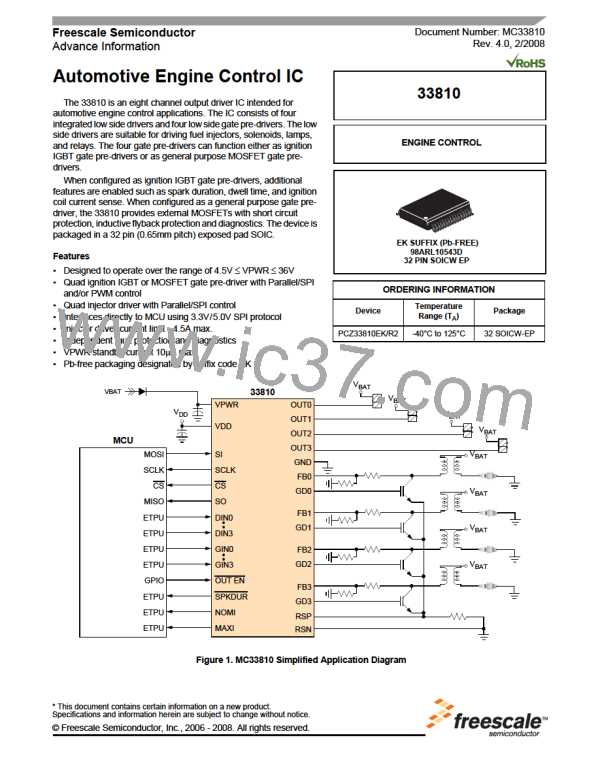

INTERNAL BLOCK DIAGRAM

INTERNAL BLOCK DIAGRAM

VPWR

VDD

VPWR, VDD

V8.0 Analog

V2.5 Logic

V

V

DD

DD

POR, Over-voltage

Under-voltage

~50µA

~50µA

CS

SI

LOGIC CONTROL

Oscillator

Bandgap

Bias

SCLK

OUTEN

~15µA

V

~15µA

SPI

INTERFACE

V2.5

OUT0

OUT1

OUT2

OUT3

Outputs 0 to 3

VOC1

DD

SO

Gate Control

DIN0

75µA

Current Limit

Temperature Limit

Short/Open

PARALLEL

CONTROL

~50µA

DIN1

DIN2

DIN3

+

–

R

S

~50µA

~50µA

~50µA

lLimit

Exposed

Pad

PWM

CONTROLLER

+

–

SPI

NOMI,MAXI

DAC

SPARK DURATION

FB0

FB1

FB2

FB3

+

–

SPI

GIN0

GIN1

GIN2

GIN3

Open Secondary

~50µA

+

100µA

VOC

V

−

PWR

GPGD

Only

SPARK

DAC

~50µA

~50µA

Low V

Clamp

GPGD

Clamp

GATE DRIVE

CONTROL

GD0

GD1

GD2

GD3

~50µA

VDD

+

NOMI

MAXI

–

DAC

~50µA

SPKDUR

RSP

RSN

+

–

DAC

NOMI

MAXI

Exposed Pad

GND

Figure 2. 33810 Simplified Internal Block Diagram

33810

Analog Integrated Circuit Device Data

Freescale Semiconductor

2

FREESCALE [ Freescale ]

FREESCALE [ Freescale ]