PRODUCT SPECIFICATION

FAN5066

VCCQP, which is supplied from an external 12V source

Application Information

through a series resistor or from a charge-pump circuit

powered from 5V if 12V is not available. The LODRV driver

has a power supply pin, VCCP, which can be supplied from

either the 12V or 5V source. The resulting voltages are suffi-

cient to provide the gate to source drive to the external

The FAN5066 Controller

The FAN5066 is a programmable synchronous DC-DC con-

troller IC. When designed around the appropriate external

components, the FAN5066 can be configured to deliver more

than 19A of output current. The FAN5066 functions as a

fixed frequency PWM step down regulator.

MOSFETs required in order to achieve a low R

.

DS,ON

Power Good (PWRGD)

The FAN5066 Power Good function is designed in accor-

dance with the Pentium II DC-DC converter specifications

and provides a continuous voltage monitor on the VFB pin.

The circuit compares the VFB signal to the VREF voltage

and outputs an active-low interrupt signal to the CPU should

the power supply voltage deviate more than ±12% of its

nominal setpoint. The Power Good flag provides no other

control function to the FAN5066.

Main Control Loop

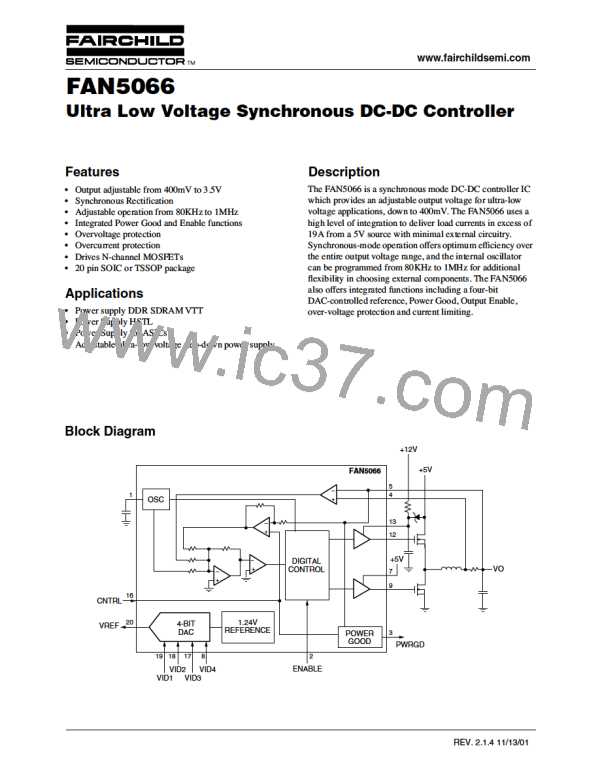

Refer to the FAN5066 Block Diagram on page 1. The

FAN5066 implements “summing mode control”, which is

different from both classical voltage-mode and current-mode

control. It provides superior performance to either by allow-

ing a large converter bandwidth over a wide range of output

loads.

The control loop of the regulator contains two main sections:

the analog control block and the digital control block. The

analog section consists of signal conditioning amplifiers

feeding into a set of comparators which provide the inputs to

the digital control block. The signal conditioning section

accepts inputs from the IFB (current feedback) and VFB

(voltage feedback) pins and sets up two controlling signal

paths. The first, the voltage control path, amplifies the differ-

ence between the VFB signal the reference voltage from the

DAC and presents the output to one of the summing ampli-

fier inputs. The second, current control path, takes the differ-

ence between the IFB and VFB pins and presents the

resulting signal to another input of the summing amplifier.

These two signals are then summed together with the slope

compensation input from the oscillator. This output is then

presented to a comparator, which provides the main PWM

control signal to the digital control block.

Output Enable (ENABLE)

The FAN5066 will accept an open collector/TTL signal for

controlling the output voltage. The low state disables the out-

put voltage. When disabled, the PWRGD output is in the low

state. If an enable is not required in the circuit, this pin may

be left open.

Over-Voltage Protection

The FAN5066 constantly monitors the output voltage for

protection against over voltage conditions. If the voltage at

the VFB pin exceeds 20% of the selected program voltage,

an over-voltage condition is assumed and the FAN5066 dis-

ables the output drive signal to the external MOSFETs. The

DC-DC converter returns to normal operation after the fault

has been removed.

Over-Current Protection

The digital control block takes the analog comparator inputs

and the main clock signal from the oscillator to provide the

appropriate pulses to the HIDRV and LODRV output pins.

These two outputs control the external power MOSFETs.

The digital block utilizes high speed Schottky transistor

logic, allowing the FAN5066 to operate at clock speeds as

high as 1MHz.

Current sense is implemented in the FAN5066 to reduce the

duty cycle of the output drive signal to the MOSFETs when

an over-current condition is detected. The voltage drop

created by the output current flowing across a sense resistor

is presented to an internal comparator. When the voltage

developed across the sense resistor exceeds the 120mV com-

parator threshold voltage, the FAN5066 reduces the output

duty cycle to help protect the power devices. The DC-DC

converter returns to normal operation after the fault has been

removed.

There are additional comparators in the analog control sec-

tion whose function is to set the point at which the FAN5066

enters its pulse skipping mode during light loads, as well as

the point at which the current limit comparator disables the

output drive signals to the external power MOSFETs.

Oscillator

The FAN5066 oscillator section uses a fixed current capaci-

tor charging configuration. An external capacitor (CEXT) is

used to set the oscillator frequency between 80KHz and

1MHz. This scheme allows maximum flexibility in choosing

external components.

High Current Output Drivers

The FAN5066 contains two identical high current output

drivers that utilize high speed bipolar transistors in a push-

pull configuration. The drivers’ power and ground are sepa-

rated from the chip’s power and ground for switching noise

immunity. The HIDRV driver has a power supply pin,

REV. 2.1.4 11/13/01

11

FAIRCHILD [ FAIRCHILD SEMICONDUCTOR ]

FAIRCHILD [ FAIRCHILD SEMICONDUCTOR ]