XRD5408/10/12

BLOCK DIAGRAM

V

REFIN

n

2

Switch

Matrix

+

-

V

OUT

R

R

AGND

V

V

DD

DD

CS

SCLK

SDIN

Shift Register

DOUT

Power On

Reset

Figure 1. Block Diagram

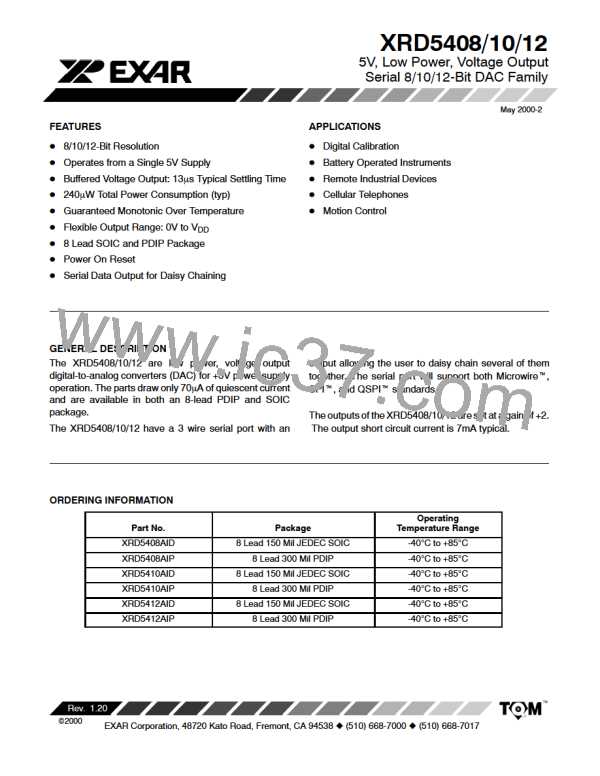

PIN CONFIGURATION

1

8

SDIN

SCLK

CS

V

V

V

DD

1

2

3

4

8

7

6

5

SDIN

SCLK

CS

V

V

V

DD

2

3

7

6

OUT

REFIN

OUT

REFIN

DOUT

AGND

4

5

DOUT

AGND

8 Lead SOIC (Jedec, 0.150”)

8 Lead PDIP (0.300”)

PIN DESCRIPTION

Pin #

Symbol

SDIN

Description

1

2

3

4

5

6

7

8

Serial Data Input

Serial Data Clock

Chip Select (Active High)

Serial Data Output

Analog Ground

SCLK

CS

DOUT

AGND

VREFIN

VOUT

VDD

Voltage Reference Input

DAC Output

Supply Voltage

Rev. 1.20

2

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]