XRD5408/10/12

DAC

n

DOUT

SDIN

MSB

X

X

X

X

Figure 6. Shift Register Format

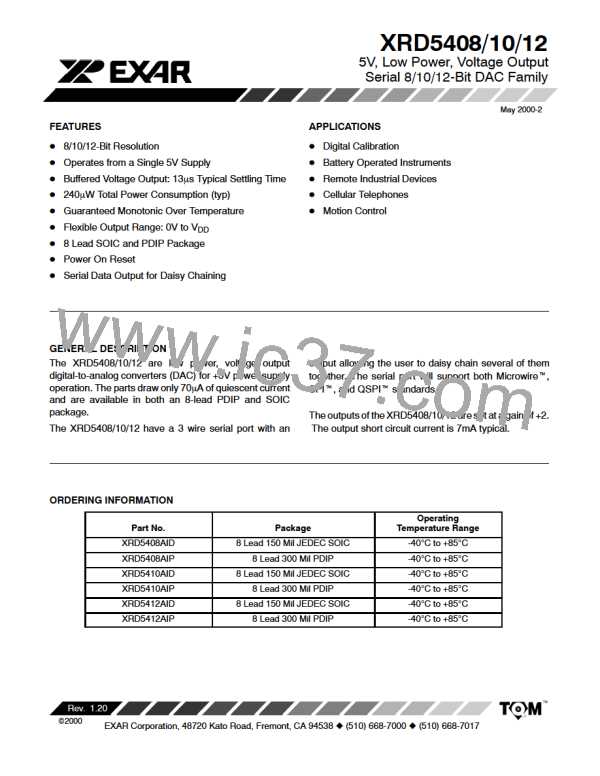

The DACs are programmedby a 16 bit word of serial data.

The format of the serial input register is shown in Figure 6.

The leading 4 bits are not used to update the DAC. If the

DAC is not daisy-chained then only a 12 bit serial word is

needed to program the DAC. The next 8, 10 or 12 bits

after the 4 leading bits are data bits. The XRD5408’s first

8 bits are valid data and the trailing 4 bits must be set to 0.

Figure 7 demonstrates the 16 bit digital word for the 8,

10,12 bit DACs.

AC Feedthrough (DAC Code = 0)

FT

AC Feedthrough from V

to V

is minimized with

REFIN

OUT

low impedance grounding as shown in Figure 7. If the

DAC data is set to all “0”s then V is a function of the

OUT

divider between the DAC string impedance and ground

impedance. See the Power Supply and Grounding

section for recommendations.

feedthrough for a 1kHz 2Vpp signal with code = 0 is

-80dB.

The typical AC

Leading

Unused

Bits

Trailing

“0”

Bits

Data Bits

MSB LSB

V

REFIN

Part

XRD5408/10/12

XXXX

XXXX

XXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

None

00

XRD5412

XRD5410

XRD5408

R

IN

0000

--

+

Table 2. 16-Bit Digital Word Register for XRD5408,

XRD5410, XRD5412.

V

OUT

GND

SCLK shouldbe held low when CS transitions low. Data is

clocked in on the rising edge of SCLK when CS is low.

SDIN data is held in a 16 bit serial shift register. The DAC

is updated with the data bits on the rising edge of CS.

When CS is high data is not shifted into the

XRD5408/10/12.

RGND

Analog GND

Daisy-Chaining

Figure 7. AC Feedthrough Equivalent

FT

The digital output port (DOUT) has a 4mA drive for greater

fan-out capability when daisy-chaining. DOUT allows

cascading of multiple DACs with the same serial data

stream. The data at SDIN appears at DOUT after 16 clock

Circuit, DAC Code =0

Compatible with MAX515 & MAX539

cycles plus one clock width (t ) and a propagation delay

CH

The XRD5408/10/12 family of DACs are functionally

campatible with the MAX515 & MAX539 while providing

significant improvements. The XRD5408/10/12 DACs

have lower power, faster serial ports, and a constant

reference impedance to minimize the reference driving

requirements and maximize system linearity. The DOUT

(t ). DOUT remains in the state of the last data bit when

DO

CS is high. DOUT changes on the falling edge of SCLK

when CS is low.

Any number of DACs can be connected in this way by

connecting DOUT of one DAC to SDIN of the next DAC.

Rev. 1.20

9

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]