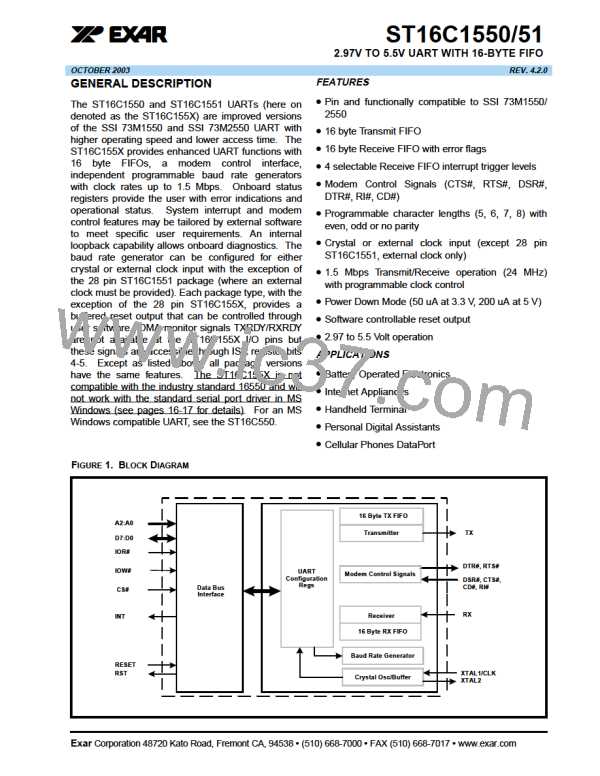

ST16C1550/51

REV. 4.2.0

áç

2.97V TO 5.5V UART WITH 16-BYTE FIFO

TABLE OF CONTENTS

GENERAL DESCRIPTION .................................................................................................1

FEATURES .....................................................................................................................................................1

APPLICATIONS................................................................................................................................................1

FIGURE 1. BLOCK DIAGRAM ............................................................................................................................................................. 1

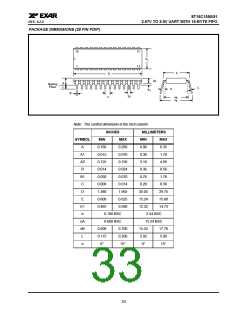

FIGURE 2. ST16C1550 PINOUTS ..................................................................................................................................................... 2

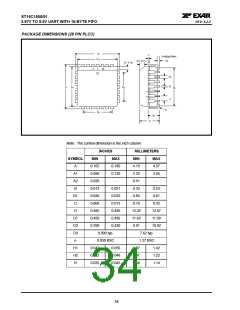

FIGURE 3. ST16C1551 PINOUTS ..................................................................................................................................................... 3

ORDERING INFORMATION.................................................................................................................................4

PIN DESCRIPTIONS .........................................................................................................5

DATA BUS INTERFACE .............................................................................................................................................5

MODEM OR SERIAL I/O INTERFACE........................................................................................................................5

ANCILLARY SIGNALS................................................................................................................................................6

1.0 PRODUCT DESCRIPTION .....................................................................................................................7

Enhanced Features .....................................................................................................................................................7

.....................................................................................................................................................................................7

Data Rate ....................................................................................................................................................................7

2.0 FUNCTIONAL DESCRIPTIONS .............................................................................................................8

2.1 INTERNAL REGISTERS ................................................................................................................................... 8

2.2 DMA MODE ....................................................................................................................................................... 8

2.3 CRYSTAL OSCILLATOR OR EXTERNAL CLOCK ......................................................................................... 8

TABLE 1: TXRDY AND RXRDY BITS IN FIFO AND DMA MODE ........................................................................................................ 8

2.4 PROGRAMMABLE BAUD RATE GENERATOR ............................................................................................. 9

FIGURE 4. TYPICAL OSCILLATOR CONNECTIONS................................................................................................................................. 9

2.5 TRANSMITTER ............................................................................................................................................... 10

2.5.1 TRANSMIT HOLDING REGISTER (THR) - WRITE ONLY......................................................................................... 10

2.5.2 TRANSMITTER OPERATION IN NON-FIFO MODE .................................................................................................. 10

TABLE 2: TYPICAL DATA RATES WITH A 14.7456 MHZ CRYSTAL OR EXTERNAL CLOCK ...................................................................... 10

2.5.3 TRANSMITTER OPERATION IN FIFO MODE ........................................................................................................... 11

2.6 RECEIVER ...................................................................................................................................................... 11

2.6.1 RECEIVE HOLDING REGISTER (RHR) - READ-ONLY ............................................................................................ 11

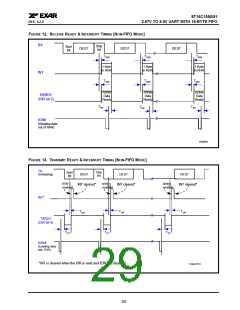

FIGURE 5. TRANSMITTER OPERATION IN NON-FIFO MODE .............................................................................................................. 11

2.7 SPECIAL (ENHANCED FEATURE) MODE .................................................................................................... 12

2.7.1 SOFT RESET .............................................................................................................................................................. 12

2.7.2 POWER DOWN MODE ............................................................................................................................................... 12

2.7.3 TXRDY AND RXRDY BITS ......................................................................................................................................... 12

2.8 INTERNAL LOOPBACK ................................................................................................................................ 12

FIGURE 6. RECEIVER OPERATION IN NON-FIFO MODE.................................................................................................................... 12

FIGURE 7. INTERNAL LOOPBACK..................................................................................................................................................... 13

3.0 UART INTERNAL REGISTERS ...........................................................................................................14

TABLE 3: ST16C155X UART INTERNAL REGISTERS ............................................................................................................... 14

TABLE 4: INTERNAL REGISTERS DESCRIPTION. SHADED BITS ARE ENABLED WHEN EFR BIT-4=1......................................... 15

4.0 INTERNAL REGISTER DESCRIPTIONS .............................................................................................16

4.1 RECEIVE HOLDING REGISTER (RHR) - READ- ONLY ............................................................................... 16

4.2 TRANSMIT HOLDING REGISTER (THR) - WRITE-ONLY ............................................................................ 16

4.3 INTERRUPT ENABLE REGISTER (IER) - READ/WRITE .............................................................................. 16

4.3.1 IER VERSUS RECEIVE FIFO INTERRUPT MODE OPERATION ............................................................................. 16

4.3.2 IER VERSUS RECEIVE/TRANSMIT FIFO POLLED MODE OPERATION................................................................ 16

4.4 INTERRUPT STATUS REGISTER (ISR) - READ-ONLY ............................................................................... 17

4.4.1 INTERRUPT GENERATION: ...................................................................................................................................... 17

4.4.2 INTERRUPT CLEARING: ........................................................................................................................................... 17

4.5 FIFO CONTROL REGISTER (FCR) - WRITE-ONLY ...................................................................................... 18

TABLE 5: INTERRUPT SOURCE AND PRIORITY LEVEL ....................................................................................................................... 18

4.6 LINE CONTROL REGISTER (LCR) - READ/WRITE ...................................................................................... 19

TABLE 6: TRANSMIT AND RECEIVE FIFO TRIGGER LEVEL SELECTION .............................................................................................. 19

TABLE 7: PARITY SELECTION .......................................................................................................................................................... 20

4.7 MODEM CONTROL REGISTER (MCR) OR GENERAL PURPOSE OUTPUTS CONTROL - READ/WRITE 21

4.8 LINE STATUS REGISTER (LSR) - READ ONLY ........................................................................................... 22

4.9 MODEM STATUS REGISTER (MSR) - READ ONLY .................................................................................... 23

4.10 SCRATCH PAD REGISTER (SPR) - READ/WRITE .................................................................................... 23

TABLE 8: UART RESET CONDITIONS........................................................................................................................................ 24

I

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]