EM6603

9

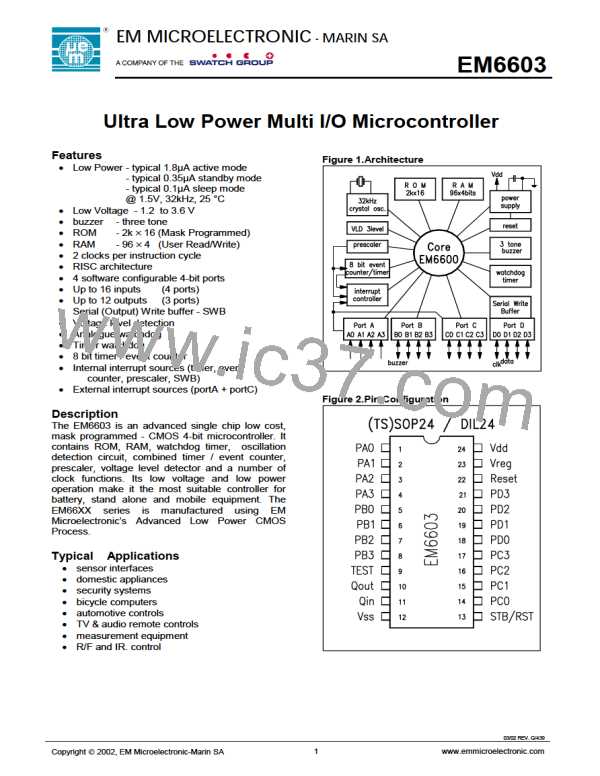

Interrupt Controller

The EM6603 has six different interrupt sources, each of which is maskable. These are:

External (3)

Internal (3)

- PortA PA3..PA0 inputs

- PortC PC3..PC0 inputs

- combined AND of PortA * PortC

- Prescaler (32Hz / 8Hz / 1Hz)

- Timer/Event counter

- SWB in interactive mode

For an interrupt to the CPU to be generated, the interrupt request flag must be set (INTxx), and the

corresponding mask register bit must be set to 1 (Mxx), the general interrupt enable flag (INTEN) must also be

set to 1. The interrupt request can be masked by the corresponding interrupt mask registers MPortx for each

input interrupt and by PSF0 ,PSF1 and MTim for internal interrupts. At initial reset the interrupt mask bits are

set to 0. INTEN bit is set automatically to 1 by Halt Instruction except when starting the Automatic SWB transfer

(see Serial Write Buffer (SWB) chapter 11)

The CPU is interrupted when one of the interrupt request flags is set to 1 in register IntRq and the INTEN bit is

enabled in the control register CIRQD. INTTE and INTPR flags are cleared automatically after a read of the

IntRq register. The other two interrupt flags INTPA (IRQ from PortA) and INTPC (IRQ from PortC) in the IntRq

register are cleared only after reading the corresponding Port interrupt request registers IRQpA and IRQpC. At

the Power on reset and in SLEEP mode the INTEN bit is also set to 0 therefore not allowing any interrupt

requests to the CPU until it is set to 1 by software.

Since the CPU has only one interrupt subroutine and because the IntRq register is cleared after reading, the

CPU does not miss any of the interrupt requests which come during the interrupt service routine. If any occur

during this time a new interrupt will be generated as soon as the CPU comes out of the current interrupt

subroutine. Interrupt priority can be controlled through software by deciding which flag in the IntRq register

should be serviced first.

For SWB interactive mode interrupt see section 11.0 Serial Write Buffer.

9.1 Interrupt control registers

Table 30.Main Interrupt request register - IntRq (Read Only)*

Bit

Name

INTPR

INTTE

INTPC

INTPA

SLEEP

Reset

R/W

Description

3

0

0

0

0

0

R

Prescaler interrupt request

Timer/counter interrupt request

PortC Interrupt request

PortA Interrupt request

SLEEP mode flag

2

R

1

R

0

R

2

W*

* Write bit 2 only if SLmask=1

If the SLEEP flag is written with 1 then the EM6603 goes immediately into SLEEP mode (SLmask was at 1).

03/02 REV. G/439

18

www.emmicroelectronic.com

Copyright 2001, EM Microelectronic-Marin SA

EMMICRO [ EM MICROELECTRONIC - MARIN SA ]

EMMICRO [ EM MICROELECTRONIC - MARIN SA ]