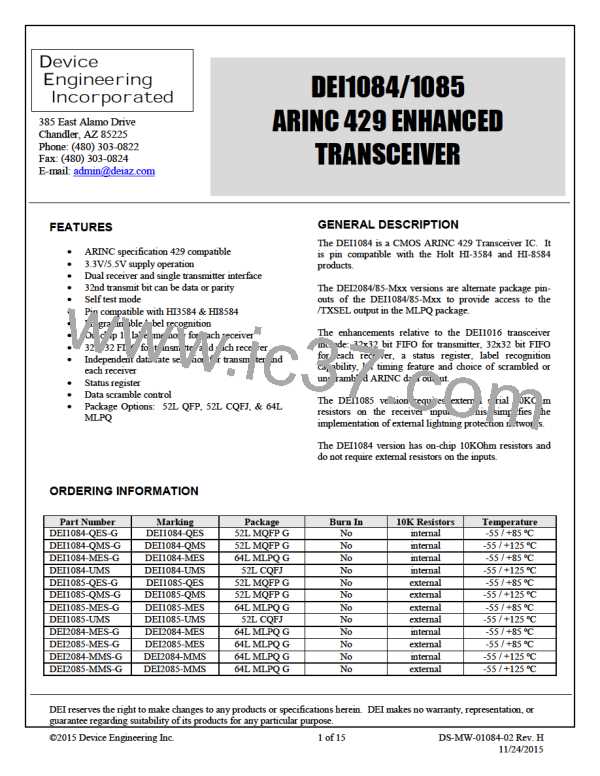

PARAMETER

SYMBOL MIN

CONTROL WORD TIMING

TYP

MAX UNITS

Pulse Width: /CWSTR tCWSTR

Setup: DATA BUS Valid to /CWSTR Hi tCWSET

80

60

40

ns

ns

ns

Hold: /CWSTR Hi to DATA BUS Hi-Z

tCWHLD

RECEIVER FIFO AND LABEL READ TIMING

Delay: Start ARINC 32nd bit to /DR Lo:

High Speed

Low Speed

Delay: /DR Lo to /EN Lo

Delay: /EN Hi to /DR Hi

Setup: SEL to /EN Lo

Hold: SEL to /EN Hi

Delay: /EN Lo to DATA BUS Valid

Delay: /EN Hi to DATA BUS Hi-Z

Pulse Width: /EN1 or /EN2

Spacing: /EN Hi to next /EN Lo (Same ARINC Word)

Spacing: /EN Hi to next /EN Lo (Next ARINC Word)

tD/R

tD/R

16

128

µs

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

tD/REN

tEND/R

tSELEN

tENSEL

tENDATA

tDATAEN

tEN

0

20

80

100

20

20

140

100

120

140

1033

tENEN

tREADEN

TRANSMITTER FIFO AND LABEL WRITE TIMING

Pulse Width: /PL1 or /PL2

tPL

tDWSET

tDWHLD

tPL12

tLABEL

tTX/R

80

60

40

40

60

ns

ns

ns

ns

ns

ns

Setup: DATA BUS Valid to/PL Hi

Hold: /PL Hi to DATA BUS Hi-Z

Spacing: /PL1 to /PL2

Spacing between Label Write pulses

Delay: /PL2 Hi to TX/R Lo

100

50

TRANSMISSION TIMING

Spacing: /PL2 Hi to ENTX Hi

Delay: 32nd ARINC Bit to TX/R Hi

Spacing: TX/R Hi to ENTX Lo

tPL2EN

tDTX/R

tENTX/R

0

0

ns

ns

ns

REPEATER OPERATION TIMING

Delay: /EN Lo to /PL Lo

Hold: /PL Hi to /EN Hi

Delay: TX/R Lo to ENTX Hi

MASTER RESET PULSE WIDTH

ARINC DATA RATE AND BIT TIMING

tENPL

tPLEN

tTX/REN

tMR

0

0

0

50

ns

ns

ns

ns

± 1%

ABSOLUTE MAXIMUM RATINGS

Table 10: Absolute Maximum Ratings

SYMBOL MIN

PARAMETER

MAX

UNITS

Supply Voltage

VDD

-0.5

-0.6

+7.0

V

V

DC Input Voltage, Logic inputs

VIN-logic

VCC

+ 0.6

DC Input Voltage, RX pins:

RIN[1A/1B/2A/2B] aka DI[1A/1B/2A/2B]

RIN[1A/1B/2A/2B]E aka DI[1A/1B/2A/2B]E at external 10K VIN-rxe

ohm series resistor

VIN-rx

±120

±120

V

Clamp diode current, any pin except RX inputs

±25

±25

mA

mA

mA

°C

DC Output Current per pin

DCV or GND current per pin

±50

Storage Temperature

Tstg

-65

+150

+145

Junction Temperature, operating

TJmax

°C

©2015 Device Engineering Inc.

13 of 15

DS-MW-01084-02 Rev. H

11/24/2015

DEIAZ [ Device Engineering Incorporated ]

DEIAZ [ Device Engineering Incorporated ]