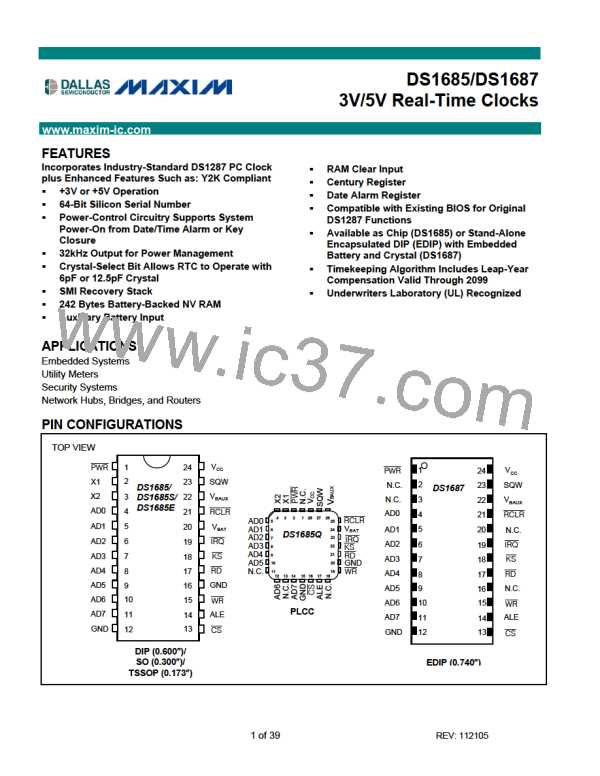

DS1685/DS1687 3V/5V Real-Time Clocks

LSB

Register B (0Bh)

MSB

BIT 7

BIT 6

PIE

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

SET

AIE

UIE

SQWE

DM

24/12

DSE

SET – When the SET bit is a 0, the update transfer functions normally by advancing the counts once per second.

When the SET bit is written to a 1, any update transfer is inhibited and the program can initialize the time and

calendar bytes without an update occurring in the midst of initializing. Read cycles can be executed in a similar

manner. SET is a read/write bit that is not modified by internal functions of the DS1685/DS1687.

PIE – The periodic-interrupt enable bit is a read/write bit that allows the periodic-interrupt flag (PF) bit in Register C

to drive the IRQ pin low. When the PIE bit is set to 1, periodic interrupts are generated by driving the IRQ pin low at

a rate specified by the RS3–RS0 bits of Register A. A 0 in the PIE bit blocks the IRQ output from being driven by a

periodic interrupt, but the periodic flag (PF) bit is still set at the periodic rate. PIE is not modified by any internal

DS1685/DS1687 functions.

AIE – The alarm-interrupt enable (AIE) bit is a read/write bit which, when set to a 1, permits the alarm flag (AF) bit

in Register C to assert IRQ. An alarm interrupt occurs for each second that the three time bytes equal the three

alarm bytes, including a “don’t care” alarm code of binary 11XXXXXX. When the AIE bit is set to 0, the AF bit does

not initiate the IRQ signal. The internal functions of the DS1685/DS1687 do not affect the AIE bit.

UIE – The update-ended interrupt-enable (UIE) bit is a read/write bit that enables the update-end flag (UF) bit in

Register C to assert IRQ. The SET bit going high clears the UIE bit.

SQWE – When the square-wave enable (SQWE) bit is set to a 1 and E32K = 0, a square-wave signal at the

frequency set by the rate-selection bits RS3–RS0 is driven out on the SQW pin. When the SQWE bit is set to 0 and

E32K = 0, the SQW pin is held low. SQWE is a read/write bit.

DM – The data mode (DM) bit indicates whether time and calendar information is in binary or BCD format. The DM

bit is set by the program to the appropriate format and can be read as required. This bit is not modified by internal

functions. A 1 in DM signifies binary data while a 0 in DM specifies BCD data.

24/12 – The 24/12 control bit establishes the format of the hours byte. A 1 indicates the 24-hour mode and a 0

indicates the 12-hour mode. This bit is read/write.

DSE - The Daylight Savings Enable (DSE) bit is a read/write bit that enables two daylight savings adjustments

when DSE is set to 1. On the first Sunday in April the time increments from 1:59:59 AM to 3:00:00 AM. On the last

Sunday in October when the time first reaches 1:59:59 AM it changes to 1:00:00 AM. When DSE is enabled, the

internal logic tests for the first/last Sunday condition at 1:59:59 AM. If the DSE bit is not set when the test occurs,

the daylight savings function will not operate correctly. These adjustments do not occur when the DSE bit is a

zero. This bit is not affected by internal functions.

13 of 39

DALLAS [ DALLAS SEMICONDUCTOR ]

DALLAS [ DALLAS SEMICONDUCTOR ]