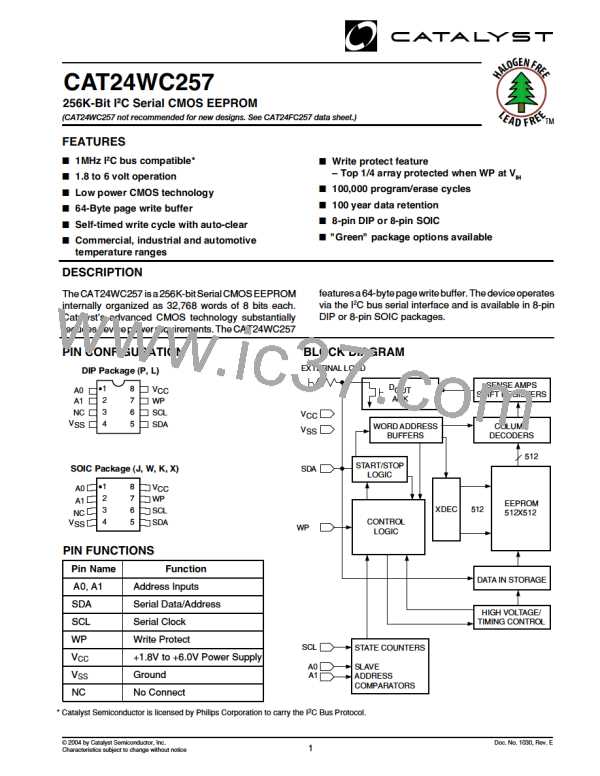

CAT24WC257

wishes to read. After CAT24WC257 acknowledges, the

MasterdevicesendstheSTARTconditionandtheslave

address again, this time with the R/W bit set to one. The

CAT24WC257 then responds with its acknowledge and

sends the 8-bit byte requested. The master device does

not send an acknowledge but will generate a STOP

condition.

READ OPERATIONS

The READ operation for the CAT24WC257 is initiated in

the same manner as the write operation with one excep-

tion, that R/W bit is set to one. Three different READ

operations are possible: Immediate/Current Address

READ,Selective/RandomREADandSequentialREAD.

Immediate/Current Address Read

Sequential Read

The CAT24WC257’s address counter contains the ad-

dress of the last byte accessed, incremented by one. In

other words, if the last READ or WRITE access was to

address N, the READ immediately following would ac-

cess data from address N+1. If N=E (where E=32767),

then the counter will ‘wrap around’ to address 0 and

continue to clock out data. After the CAT24WC257

receives its slave address information (with the R/W bit

set to one), it issues an acknowledge, then transmits the

8 bit byte requested. The master device does not send

an acknowledge, but will generate a STOP condition.

The Sequential READ operation can be initiated by

either the Immediate Address READ or Selective READ

operations. After the CAT24WC257 sends the initial 8-

bit byte requested, the Master will respond with an

acknowledge which tells the device it requires more

data. The CAT24WC257 will continue to output an 8-bit

byte for each acknowledge sent by the Master. The

operationwillterminatewhentheMasterfailstorespond

with an acknowledge, thus sending the STOP condition.

The data being transmitted from CAT24WC257 is out-

puttedsequentiallywithdatafromaddressNfollowedby

data from address N+1. The READ operation address

counterincrementsalloftheCAT24WC257addressbits

so that the entire memory array can be read during one

operation. If more than E (where E=32767) bytes are

read out, the counter will ‘wrap around’ and continue to

clock out data bytes.

Selective/Random Read

Selective/Random READ operations allow the Master

device to select at random any memory location for a

READ operation. The Master device first performs a

‘dummy’ write operation by sending the START condi-

tion, slave address and byte addresses of the location it

Figure 8. Immediate Address Read Timing

S

T

A

R

T

S

T

O

P

BUS ACTIVITY:

MASTER

SLAVE

ADDRESS

DATA

SDA LINE

S

P

A

C

K

N

O

A

C

K

SCL

SDA

8

9

8TH BIT

DATA OUT

NO ACK

STOP

Doc. No. 1030, Rev. E

7

CATALYST [ CATALYST SEMICONDUCTOR ]

CATALYST [ CATALYST SEMICONDUCTOR ]