3.15V

VL

Standard

Load

Thevenin

Equivalent

R1

R2

RL

Output

Output

CL

CL

Figure 8 - PEEL™ Device and Array Test Loads

Technology

R1

R2

RL

VL

CL

CMOS

TTL

1.275V

1.840V

33 pF

33 pF

284 kΩ

308 Ω

258 kΩ

433 Ω

113 kΩ

180 Ω

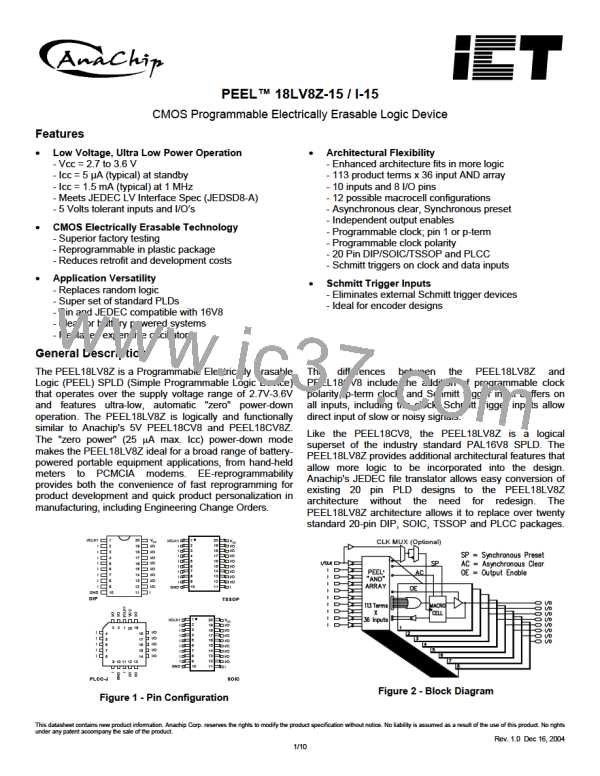

Ordering Information

Part Number

Speed

Temperature

Package

PEEL18LV8ZP-15 (L)

PEEL18LV8ZPI-15 (L)

PEEL18LV8ZJ-15 (L)

PEEL18LV8ZJI-15 (L)

PEEL18LV8ZS-15 (L)

PEEL18LV8ZSI-15 (L)

PEEL18LV8ZT-15 (L)

PEEL18LV8ZTI-15 (L)

15ns

15ns

15ns

15ns

15ns

15ns

15ns

15ns

Commercial

Industrial

20-pin Plastic DIP

20-pin Plastic DIP

20-pin PLCC

Commercial

Industrial

20-pin PLCC

Commercial

Industrial

20-pin SOIC

20-pin SOIC

Commercial

Industrial

20-pin TSSOP

20-pin TSSOP

Part Number

Device

Suffix

PEELTM18LV8Z PI-15X

Lead Free

L : Lead Free Package

Blank : Normal

Package

Speed

P = 20-pin Plastic 300mil DIP

-15 = 15ns tpd

J = 20-pin Plastic (J) Leaded Chip Carrier (PLCC)

S = 20-pin SOIC 300 mil Gullwing

T = 20-pin TSSOP 170 mil

Temperature Range

(Blank) = Commercial 0 to +70oC

I = Industrial -40 to +85oC

Anachip Corp.

www.anachip.com.tw

Rev. 1.0 Dec 16, 2004

9/10

ANACHIP [ ANACHIP CORP ]

ANACHIP [ ANACHIP CORP ]