switching long enough to trigger the next power-down. When the PEEL18LV8Z is powered up, a built-in feature

(Note that the tPD is approximately 5 ns. slower on the first holds the outputs in tri-state until Vcc reaches 2.2V. This

transition from sleep mode.)

prevents output transitions during power-up.

As a result of the "Zero-Power" feature, significant power

savings can be realized for combinatorial or sequential

operations when the inputs or clock change at a modest

rate. See Figure 6.

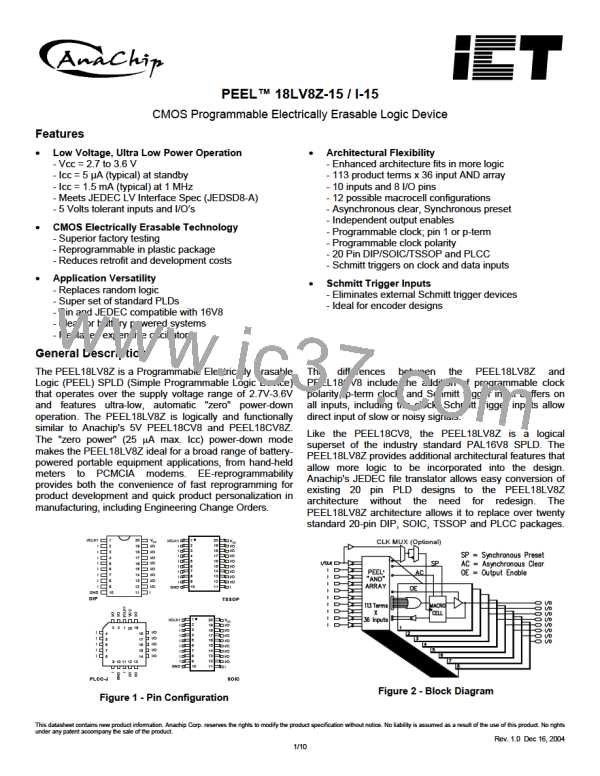

Figure 5 - Equivalent Circuits for the twelve configurations of the PEEL18LV8Z I/O Macrocell

Configuration

Input/Feedback Select

Output Select

#

A

B

C

D

1

2

3

4

5

6

7

8

9

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

1

0

0

1

1

0

0

1

1

1

1

0

0

1

1

1

1

0

0

1

1

0

0

0

0

1

1

1

1

0

0

0

0

Active Low

Register

Combinatorial

Register

Active High

Active Low

Active High

Active Low

Active High

Active Low

Active High

Active Low

Active High

Active Low

Active High

Bi-directional I/O

Combinatorial Feedback

Register Feedback

Combinatorial

Register

10

11

12

Combinatorial

Anachip Corp.

www.anachip.com.tw

Rev. 1.0 Dec 16, 2004

5/10

ANACHIP [ ANACHIP CORP ]

ANACHIP [ ANACHIP CORP ]