AS5050

Datasheet - Detailed Description

SOFTWARE RESET Command. The SOFTWARE RESET command is implemented as WRITE command. The bit ‘RES SPI’ of the DATA

package indicates if the SPI registers should be reset as well. The soft reset resets the digital part (‘RES SPI’ is set to one) as well as the OTP

memory. A new OTP memory auto-load is initiated and the reset values stored in the OTP memory are loaded into the configuration registers.

The command following the SOFTWARE RESET command can be any of the commands specified in this chapter.

After the data package is sent, the soft reset is generated. The fuses of the OTP memory are loaded into the registers and a new conversion

cycle will be started. If the device is in sleep mode the oscillator will be started first.

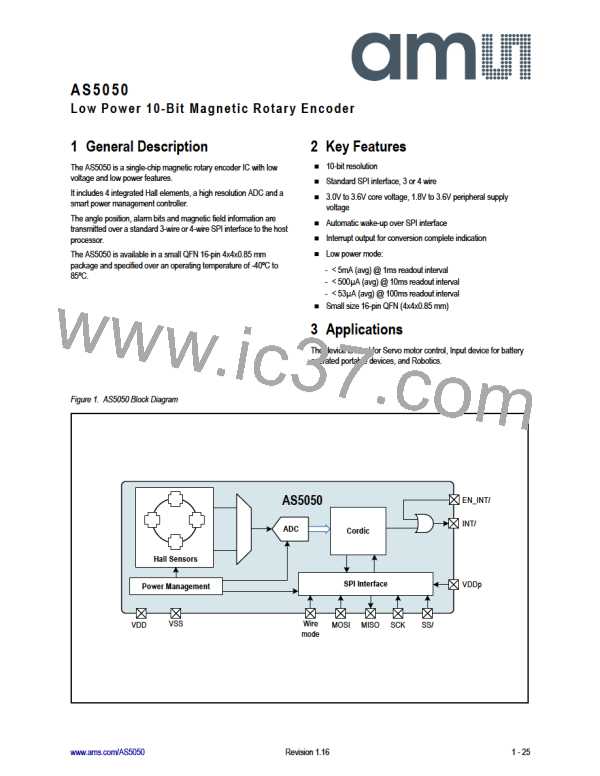

Figure 8. SOFTWARE RESET Command

T

COM

MSB

LSB

MSB

LSB

MSB

LSB

SOFTWARE

RESET

command

MOSI

MISO

DATA

Next command

Response-1

0x 0000

0x 0000

MSB

LSB

MSB

LSB

MSB

LSB

Transmission N

Transmission N +1

Transmission N +2

In order to invoke a software reset on the AS5050 the following bit pattern has to be sent.

Table 11. SOFTWARE RESET Command

Bit

MSB

14

13

12

11

10

9

8

7

6

5

4

3

2

1

LSB

PAR

PAR

0

1

1

1

1

0

0

0

0

0

0

0

0

0

0

SOFTWARE RESET command

Table 12. Data Package

Bit MSB 14

13

12

11

10

9

8

7

6

5

4

3

2

1

LSB

Don’t care

RES SPI Don’t care PAR

Bit

Description

If set to one, SPI registers are reset as well1

Parity bit (EVEN)

RES SPI

PAR

1. After a power on reset, the OTP will be read and hence OTP related

registers are changed independent on the RES SPI flag.

www.ams.com/AS5050

Revision 1.16

12 - 25

AMSCO [ AMS(艾迈斯) ]

AMSCO [ AMS(艾迈斯) ]