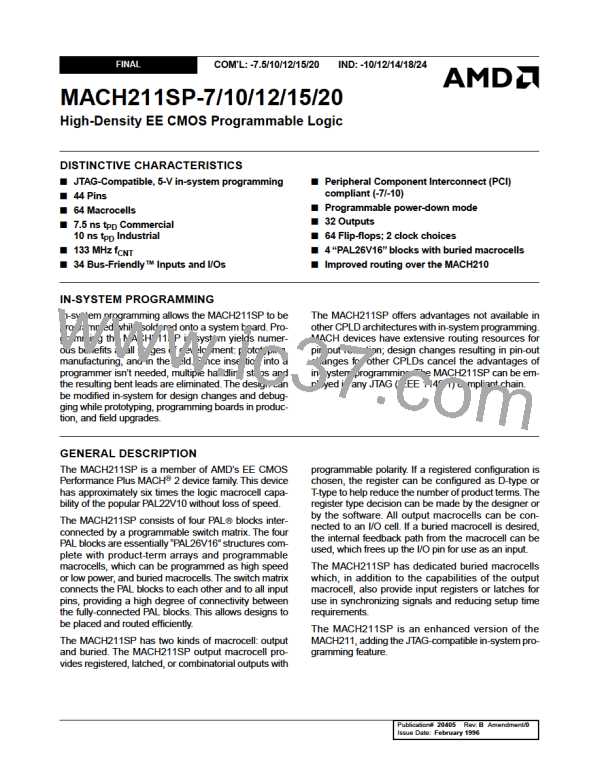

SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)

(continued)

-12

-15

-20

Parameter

Symbol

Parameter Description

Min

Max

Min

Max

Min

Max

Unit

t

Input Latch Gate to Combinatorial Output

17

20

25

ns

IGO

Input Latch Gate to Output Through Transparent

Output Latch

t

19

22

27

ns

ns

IGOL

SetupTime from Input, I/O, or FeedbackThrough

Transparent Input Latch to Output Latch Gate

t

9

12

15

SLL

t

Input Latch Gate to Output Latch Setup

Input Latch Gate Width LOW

13

6

16

6

21

8

ns

ns

IGS

t

WIGL

Input, I/O, or Feedback to Output Through

Transparent Input and Output Latches

t

16

16

19

20

24

25

ns

ns

PDLL

Asynchronous Reset to Registered or Latched

Output

t

AR

t

Asynchronous Reset Width (Note 1)

12

8

15

10

20

15

ns

ns

ARW

t

Asynchronous Reset Recovery Time (Note 1)

ARR

Asynchronous Preset to Registered or Latched

Output

t

16

20

25

ns

AP

t

Asynchronous Preset Width (Note 1)

12

8

15

10

20

15

ns

ns

ns

APW

t

Asynchronous Preset Recovery Time (Note 1)

Input, I/O, or Feedback to Output Enable (Note 1)

APR

t

15

15

15

15

15

15

EA

Input, I/O, or Feedback to Output Disable

(Note 1)

t

ns

ER

t

Increase for Powered-down Macrocell

PD

t

10

10

0

10

10

0

10

10

0

ns

ns

ns

LP

(Note 3)

t

t Increase for Powered-down Macrocell (Note 3)

LPS

S

t

Increase for Powered-down Macrocell

CO

t

LPCO

(Note 3)

t

Increase for Powered-down Macrocell

EA

t

10

10

10

ns

LPEA

(Note 3)

Notes:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified

where frequency may be affected.

2. See Switching Test Circuit for test conditions.

3. If a signal is powered-down, this parameter must be added to its respective high-speed parameter.

MACH211SP-12/15/20 (Com’l)

15

AMD [ AMD ]

AMD [ AMD ]