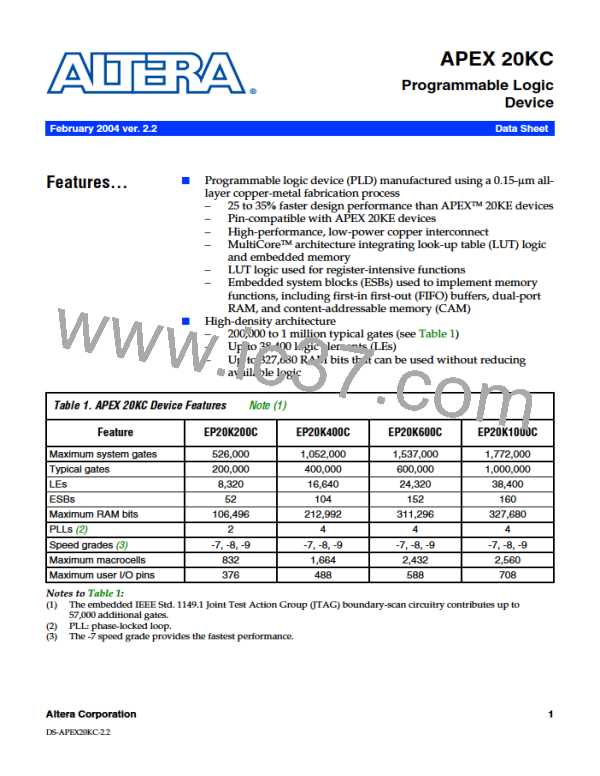

APEX 20KC Programmable Logic Device Data Sheet

The ESB can implement a variety of memory functions, including CAM,

RAM, dual-port RAM, ROM, and FIFO functions. Embedding the

memory directly into the die improves performance and reduces die area

compared to distributed-RAM implementations. Moreover, the

abundance of cascadable ESBs allows APEX 20KC devices to implement

multiple wide memory blocks for high-density designs. The ESB’s high

speed ensures it can implement small memory blocks without any speed

penalty. Additionally, designers can use the ESBs to create as many

different-sized memory blocks as the system requires. Figure 1 shows an

overview of the APEX 20KC device.

Figure 1. APEX 20KC Device Block Diagram

Clock Management Circuitry

FastTrack

Interconnect

IOE

IOE

ClockLock

IOE

LUT

IOE

LUT

LUT

IOE

Four-input LUT

for data path and

DSP functions.

LUT

LUT

IOE

Product Term

Memory

Product Term

Memory

Product Term

Memory

Product Term

Memory

IOEs support

PCI, GTL+,

SSTL-3, LVDS,

and other

Product-term

integration for

high-speed

control logic and

state machines.

standards.

LUT

LUT

LUT

Product Term

Memory

LUT

Product Term

Memory

Product Term

Memory

IOE

IOE

Product Term

Memory

Flexible integration

of embedded

memory, including

CAM, RAM,

IOE

IOE

IOE

IOE

ROM, FIFO, and

other memory

functions.

APEX 20KC devices provide four dedicated clock pins and four dedicated

input pins that drive register control inputs. These signals ensure efficient

distribution of high-speed, low-skew control signals, which use dedicated

routing channels to provide short delays and low skews. Four of the

dedicated inputs drive four global signals. These four global signals can

also be driven by internal logic, providing an ideal solution for a clock

divider or internally generated asynchronous clear signals with high

fan-out. The dedicated clock pins featured on the APEX 20KC devices can

also feed logic. The devices also feature ClockLock and ClockBoost clock

management circuitry.

8

Altera Corporation

ALTERA [ ALTERA CORPORATION ]

ALTERA [ ALTERA CORPORATION ]