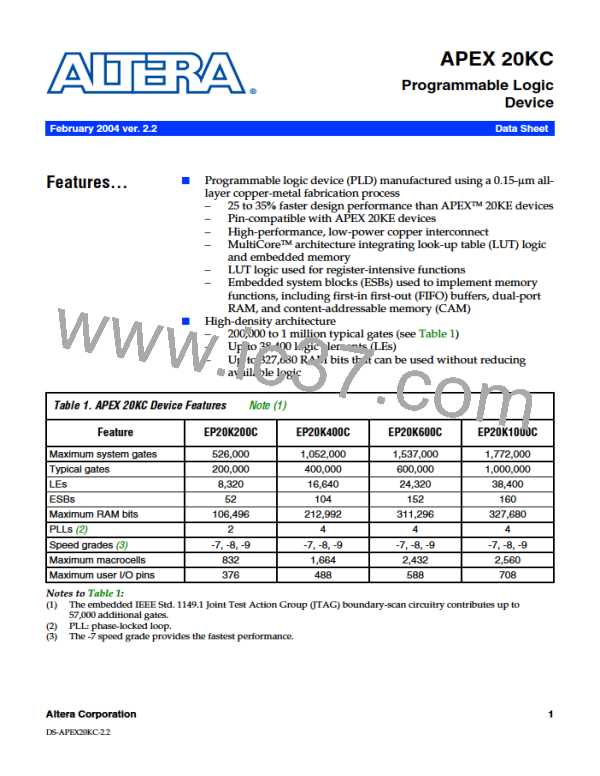

APEX 20KC Programmable Logic Device Data Sheet

The LAB-wide control signals can be generated from the LAB local

interconnect, global signals, and dedicated clock pins. The inherent low

skew of the FastTrack interconnect enables it to be used for clock

distribution. Figure 4 shows the LAB control signal generation circuit.

Figure 4. LAB Control Signal Generation

4

Dedicated

Clocks

4

Global

Signals

Local

Interconnect

Local

Interconnect

Local

Interconnect

Local

Interconnect

LABCLKENA1

SYNCLOAD

LABCLR1 (1)

or LABCLKENA2

SYNCCLR

or LABCLK2 (2)

LABCLK1

LABCLR2 (1)

Notes to Figure 4:

(1) The LABCLR1and LABCLR2signals also control asynchronous load and asynchronous preset for LEs within the

LAB.

(2) The SYNCCLRsignal can be generated by the local interconnect or global signals.

Logic Element

The LE, the smallest unit of logic in the APEX 20KC architecture, is

compact and provides efficient logic usage. Each LE contains a four-input

LUT, which is a function generator that can quickly implement any

function of four variables. In addition, each LE contains a programmable

register and carry and cascade chains. Each LE drives the local

interconnect, MegaLAB interconnect, and FastTrack interconnect routing

structures. See Figure 5.

Altera Corporation

11

ALTERA [ ALTERA CORPORATION ]

ALTERA [ ALTERA CORPORATION ]