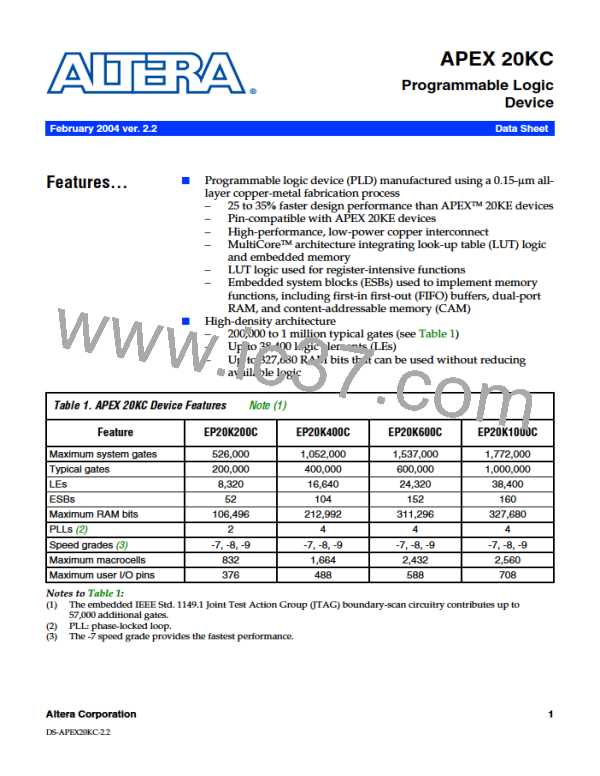

APEX 20KC Programmable Logic Device Data Sheet

Table 4. APEX 20KC FineLine BGA Package Options & I/O Count Notes (1), (2)

Device

484 Pin

672 Pin

1,020 Pin

EP20K200C

EP20K400C

EP20K600C

EP20K1000C

376

488 (3)

508 (3)

508 (3)

588

708

Notes to Tables 3 and 4:

(1) I/O counts include dedicated input and clock pins.

(2) APEX 20KC device package types include plastic quad flat pack (PQFP), 1.27-mm

pitch ball-grid array (BGA), and 1.00-mm pitch FineLine BGATM packages.

(3) This device uses a thermally enhanced package, which is taller than the regular

package. Consult the Altera Device Package Information Data Sheet for detailed

package size information.

Table 5. APEX 20KC QFP & BGA Package Sizes

Feature

208-Pin PQFP

240-Pin PQFP

356-Pin BGA

652-Pin BGA

Pitch (mm)

Area (mm2)

0.50

924

0.50

1,218

1.27

1,225

1.27

2,025

Length × Width (mm × mm)

30.4 × 30.4

34.9 × 34.9

35.0 × 35.0

45.0 × 45.0

Table 6. APEX 20KC FineLine BGA Package Sizes

Feature

484 Pin

672 Pin

1,020 Pin

Pitch (mm)

Area (mm2)

1.00

529

1.00

729

1.00

1,089

Length × Width (mm × mm)

23 × 23

27 × 27

33 × 33

Similar to APEX 20K and APEX 20KE devices, APEX 20KC devices offer

the MultiCore architecture, which combines the strengths of LUT-based

and product-term-based devices with an enhanced memory structure.

LUT-based logic provides optimized performance and efficiency for data-

path, register-intensive, mathematical, or digital signal processing (DSP)

designs. Product-term-based logic is optimized for complex

General

Description

combinatorial paths, such as complex state machines. LUT- and product-

term-based logic combined with memory functions and a wide variety of

MegaCore and AMPP functions make the APEX 20KC architecture

uniquely suited for SOPC designs. Applications historically requiring a

combination of LUT-, product-term-, and memory-based devices can now

be integrated into one APEX 20KC device.

4

Altera Corporation

ALTERA [ ALTERA CORPORATION ]

ALTERA [ ALTERA CORPORATION ]