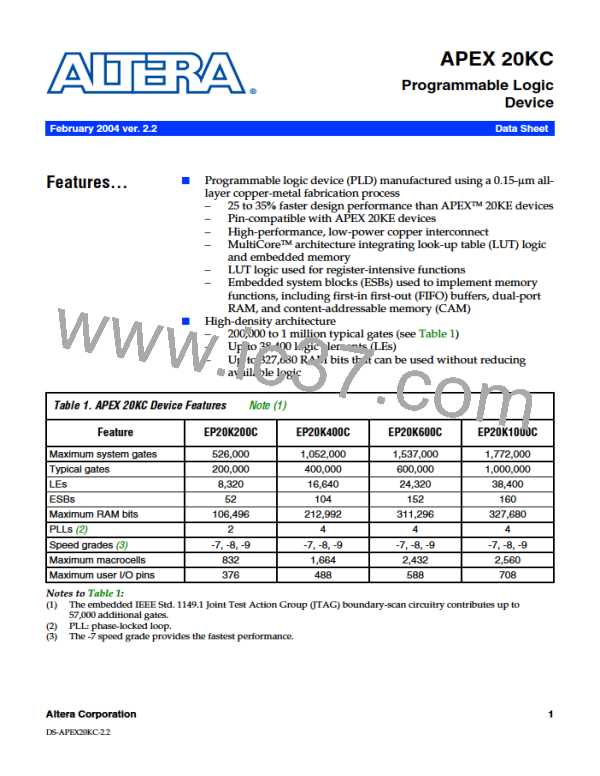

APEX 20KC Programmable Logic Device Data Sheet

■

Low-power operation design

...and More

Features

–

–

–

–

1.8-V supply voltage (see Table 2)

Copper interconnect reduces power consumption

MultiVoltTM I/O support for 1.8-V, 2.5-V, and 3.3-V interfaces

ESBs offering programmable power-saving mode

■

Flexible clock management circuitry with up to four phase-locked

loops (PLLs)

–

–

–

–

Built-in low-skew clock tree

Up to eight global clock signals

ClockLockTM feature reducing clock delay and skew

ClockBoostTM feature providing clock multiplication and

division

–

ClockShiftTM feature providing programmable clock phase and

delay shifting

■

Powerful I/O features

–

Compliant with peripheral component interconnect Special

Interest Group (PCI SIG) PCI Local Bus Specification,

Revision 2.2 for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

Support for high-speed external memories, including DDR

synchronous dynamic RAM (SDRAM) and ZBT static RAM

(SRAM)

–

–

–

16 input and 16 output LVDS channels at 840 megabits per

second (Mbps)

Direct connection from I/O pins to local interconnect providing

fast tCO and tSU times for complex logic

–

–

–

–

MultiVolt I/O support for 1.8-V, 2.5-V, and 3.3-V interfaces

Programmable clamp to VCCIO

Individual tri-state output enable control for each pin

Programmable output slew-rate control to reduce switching

noise

–

Support for advanced I/O standards, including low-voltage

differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT,

SSTL-3 and SSTL-2, GTL+, and HSTL Class I

Supports hot-socketing operation

–

–

Pull-up on I/O pins before and during configuration

Table 2. APEX 20KC Supply Voltages

Feature

Voltage

Internal supply voltage (VCCINT

)

1.8 V

MultiVolt I/O interface voltage levels (VCCIO) 1.8 V, 2.5 V, 3.3 V, 5.0 V (1)

Note to Table 2:

(1) APEX 20KC devices can be 5.0-V tolerant by using an external resistor.

2

Altera Corporation

ALTERA [ ALTERA CORPORATION ]

ALTERA [ ALTERA CORPORATION ]