September 2005

ASM5P2304B

rev 0.5

Pin Configuration

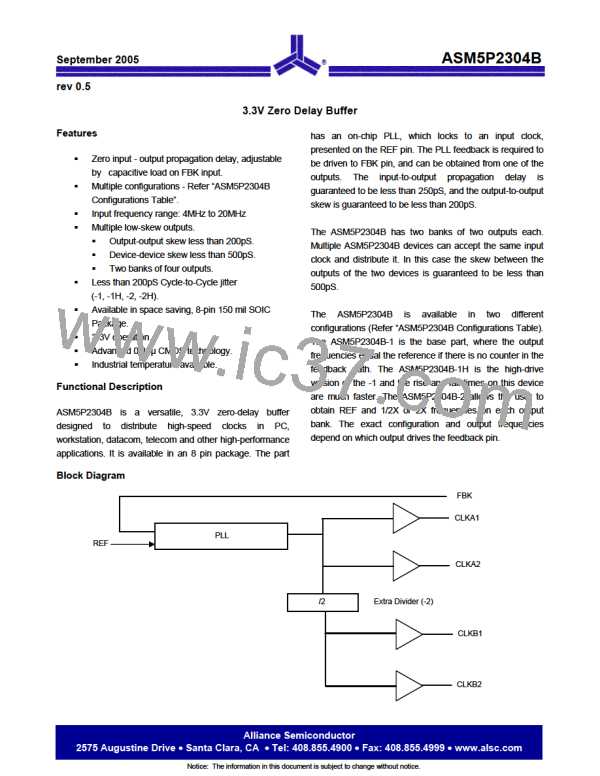

REF

CLKA1

CLKA2

GND

1

2

3

4

8

7

6

5

FBK

VDD

ASM5P2304B

CLKB2

CLKB1

Pin Description for ASM5P2304B

Pin #

Pin Name

Description

1

2

3

4

5

6

7

8

REF1

Input reference frequency, 5V tolerant input

Buffered clock output, bank A

Buffered clock output, bank A

Ground

CLKA12

CLKA22

GND

CLKB12

CLKB2 2

VDD

Buffered clock output, bank B

Buffered clock output, bank B

3.3V supply

FBK

PLL feedback input

Notes:

1. Weak pull-down.

2. Weak pull-down on all outputs.

3.3V Zero Delay Buffer

3 of 13

Notice: The information in this document is subject to change without notice.

ALSC [ ALLIANCE SEMICONDUCTOR CORPORATION ]

ALSC [ ALLIANCE SEMICONDUCTOR CORPORATION ]