ASAHI KASEI

[AK4115]

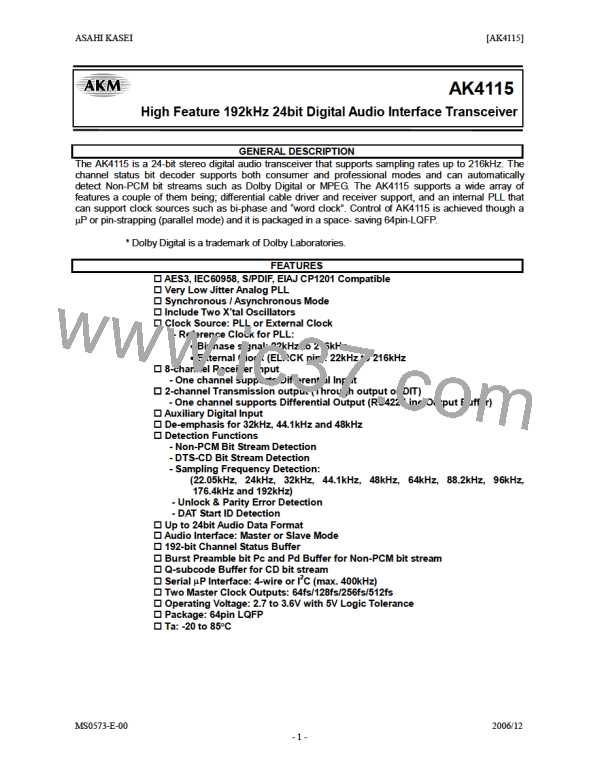

SWITCHING CHARACTERISTICS

(Ta=25°C; AVDD, OVDD, DVDD=2.7~3.6V, TVDD=2.7~5.5V; CL=20pF)

Parameter

Symbol

min

typ

max

Units

Master Clock Timing

Crystal Resonator

External Clock

Frequency

Frequency

Duty

Frequency

Duty

fXTAL

fECLK

dECLK

fMCK1

dMCK1

fMCK2

dMCK2

fpll

11.2896

11.2896

40

2.816

40

1.408

40

22

-

-

50

-

50

-

50

-

-

-

24.576

27.648

60

27.648

60

27.648

60

216

MHz

MHz

%

MHz

%

MHz

%

kHz

kHz

%

MCKO1 Output

MCKO2 Output

Frequency

Duty

PLL Clock Recover Frequency (RX7-0)

LRCK Frequency

Duty Cycle (at Slave Mode)

Duty Cycle (at Master Mode)

Audio Interface Timing 1

Slave Mode

fs

dLCK

dLCK

22

45

-

216

55

-

50

%

BICK Period

BICK Pulse Width Low

Pulse Width High

LRCK Edge to BICK “ ” (Note 11)

tBCK

tBCKL

tBCKH

tLRB

72

27

27

15

15

-

-

-

-

15

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

20

20

25

25

-

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

↑

tBLR

BICK “ ” to LRCK Edge (Note 11)

↑

tLRM

tBSD

tLRM

tBSD

tDXH

tDXS

(3.0V ≤ DVDD,OVDD ≤ 3.6V)

LRCK to SDTO (MSB)

BICK “ ” to SDTO

(3.0V ≤ DVDD,OVDD ≤ 3.6V)

(2.7V ≤ DVDD,OVDD < 3.0V)

↓

LRCK to SDTO (MSB)

BICK “↓” to SDTO

DAUX Hold Time

DAUX Setup Time

Master Mode

(2.7 V≤ DVDD,OVDD < 3.0V)

15

-

BICK Frequency

BICK Duty

fBCK

dBCK

tMBLR

tBSD

-

-

-15

-

64fs

50

-

-

-

-

15

15

-

Hz

%

ns

ns

ns

BICK “↓” to LRCK

BICK “↓” to SDTO

DAUX Hold Time

DAUX Setup Time

Master Clock Timing 2

EMCK

tDXH

15

-

tDXS

15

-

-

ns

Frequency

Duty

PLL Lock Range

Frequency

Duty

fECLK2

dECLK2

fEPLL

fs

2.816

40

22

22

40

-

50

-

-

50

27.648

60

216

216

60

MHz

%

kHz

kHz

%

ELRCK

dLCK

Audio Interface Timing 2

Slave Mode

EBICK Period

EBICK Pulse Width Low

Pulse Width High

ELRCK Edge to BICK “↑”

EBICK “↑” to ELRCK Edge

DAUX Hold Time

DAUX Setup Time

Master Mode

tEBCK

tEBCKL

tEBCKH

tELRB

tEBLR

tEDXH

tEDXS

72

27

27

15

15

15

15

-

-

-

-

-

-

-

-

-

-

-

-

-

-

ns

ns

ns

ns

ns

ns

ns

(Note 12)

(Note 12)

EBICK Frequency

EBICK Duty

EBICK “↓” to ELRCK

DAUX Hold Time

DAUX Setup Time

fEBCK

dEBCK

tEMBLR

tEDXH

tEDXS

-

-

-15

15

15

64fs

50

-

-

-

-

-

15

-

Hz

%

ns

ns

ns

-

Note 11. BICK rising edge must not occur at the same time as LRCK edge.

Note 12. EBICK rising edge must not occur at the same time as ELRCK edge.

MS0573-E-00

2006/12

- 10 -

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]