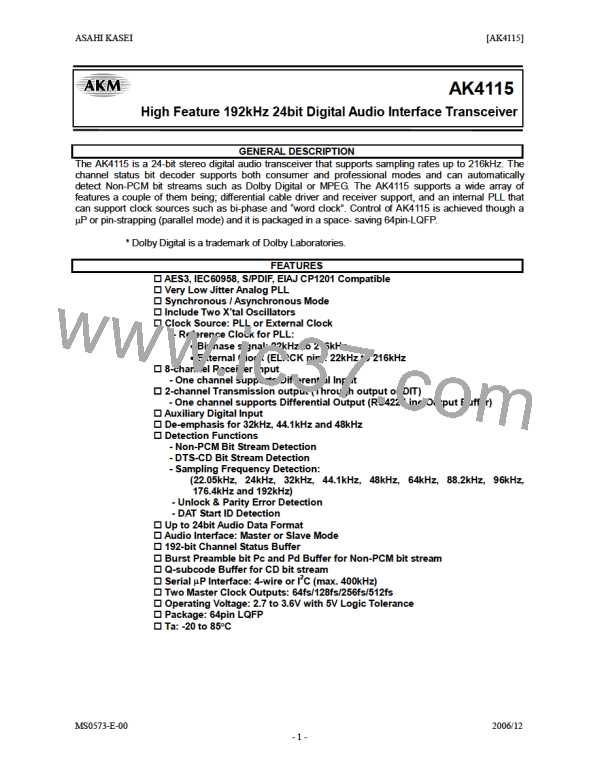

ASAHI KASEI

[AK4115]

PIN/FUNCTION (Continued)

Function

No.

37

Pin Name

CM0

CDTO

CAD1

CM1

I/O

I

O

I

I

I

Master Clock Operation Mode #0 Pin in parallel mode

Control Data Output Pin in serial mode, IIC pin = “L”.

Chip Address #1 Pin in serial mode, IIC pin = “H”.

Master Clock Operation Mode #1 Pin in parallel mode

Control Data Input Pin in serial mode, IIC pin = “L”.

Control Data Pin in serial mode, IIC pin = “H”.

An external pull-up resistor is required.

Output Clock Select #1 Pin in parallel mode

Control Data Clock Pin in serial mode, IIC pin = “L”

Control Data Clock Pin in serial mode, IIC pin = “H”

An external pull-up resistor is required.

Output Clock Select #0 Pin in parallel mode

Chip Select Pin in serial mode, IIC pin = “L”.

Chip Address #0 Pin in serial mode, IIC pin = “H”.

Digital Power Supply Pin, 3.3V

CDTI

38

SDA

I/O

OCKS1

CCLK

I

I

39

40

SCL

I

OCKS0

CSN

I

I

I

-

-

-

I

CAD0

DVDD

DVSS

BVSS

IPS1

41

42

43

Digital Ground Pin

Substrate Ground Pin

Input Channel Select #1 Pin in parallel mode

IIC Select Pin in serial mode

44

45

IIC

I

“L”: 4-wire Serial, “H”: I2C

PLL Source Select Pin

PSEL

I

“L”: S/PDIF Input, “H”: ELRCK Input Clock

PSEL pin and PSEL bit are ORed in serial mode.

X’tal Frequency Select #0 Pin

X’tal Frequency Select #1 Pin

PLL Loop Filter Pin

46

47

48

49

XTL0

XTL1

FILT

I

I

O

-

AVSS

Analog Ground Pin

External Resistor Pin

50

R

O

10k

1% resistor should be connected to AVSS externally.

Ω ±

Common Voltage Output Pin

51

52

53

VCOM

AVDD

P/SN

O

-

4.7µF capacitor should be connected to AVSS externally.

Analog Power Supply Pin, 3.3V

Parallel/Serial Select Pin

“L”: Serial Mode, “H”: Parallel Mode

Master Clock Frequency Auto Setting Mode Pin.

“L”: Disable, “H”: Enable

I

54

ACKS

I

ACKS pin and ACKS bit are ORed in serial mode.

Receiver Channel #0 Negative Input Pin

In serial mode, this channel is selected as default channel.

Receiver Channel #0 Positive Input Pin

In serial mode, this channel is selected as default channel.

(Internal biased pin)

55

56

RXN0

RXP0

I

I

(Internal biased pin)

57

58

59

60

61

62

63

AVSS

RX1

AVDD

RX2

AVSS

RX3

AVDD

IPS0

-

I

-

I

-

I

-

I

I

Analog Ground Pin

Receiver Channel #1 Pin

Analog Power Supply Pin, 3.3V

Receiver Channel #2 Pin

Analog Ground Pin

(Internal biased pin)

(Internal biased pin)

(Internal biased pin)

Receiver Channel #3 Pin

Analog Power Supply Pin, 3.3V

Input Channel Select #0 Pin in parallel mode

Receiver Channel #4 Pin in serial mode

64

RX4

(Internal biased pin)

Note 1. Do not allow digital input pins except internal biased pins to float.

MS0573-E-00

2006/12

- 6 -

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]