ADM8690–ADM8695

Table I. AD M8691, AD M8693, AD M8695 Reset P ulse Width and Watchdog Tim eout Selections

Watchdog Tim eout P eriod

Im m ediately

Reset Active P eriod

O SC SEL

O SC IN

Norm al

After Reset

AD M8691/AD M8693

AD M8695

Low

Low

External Clock Input

External Capacitor

1024 CLKS

400 ms × C/47 pF

100 ms

4096 CLKS

1.6 s × C/47 pF

1.6 s

512 CLKS

200 ms × C/47 pF

50 ms

2048 CLKS

520 ms × C/47 pF

200 ms

Floating or High Low

Floating or High Floating or High

1.6 s

1.6 s

50 ms

200 ms

NOT E

With the OSC SEL pin low, OSC IN can be driven by an external clock signal, or an external capacitor can be connected between OSC IN and GND. T he nominal

internal oscillator frequency is 10.24 kHz. T he nominal oscillator frequency with external capacitor is: F OSC (Hz) = 184,000/C (pF)

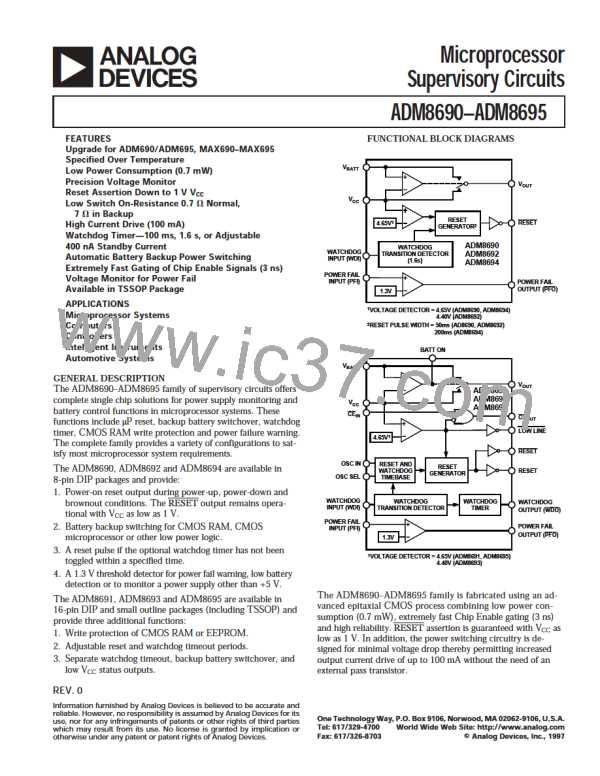

On the ADM8690/ADM8692 the watchdog timeout period is

fixed at 1.6 seconds and the reset pulse width is fixed at 50 ms.

On the ADM8694 the watchdog timeout period is also 1.6 sec-

onds but the reset pulse width is fixed at 200 ms. The ADM8691/

ADM8693/ADM8695 allow these times to be adjusted as

shown in T able I. Figure 4 shows the various oscillator configu-

rations that can be used to adjust the reset pulse width and

watchdog timeout period.

8

7

OSC SEL

ADM8691

ADM8693

ADM8695

OSC IN

C

OSC

Figure 4b. External Capacitor

T he internal oscillator is enabled when OSC SEL is high or

floating. In this mode, OSC IN selects between the 1.6 second

and 100 ms watchdog timeout periods. With OSC IN connected

high or floating, the 1.6 second timeout period is selected; while

with it connected low, the 100 ms timeout period is selected. In

either case, immediately after a reset the timeout period is 1.6

seconds. T his gives the microprocessor time to reinitialize the

system. If OSC IN is low, then the 100 ms watchdog period be-

comes effective after the first transition of WDI. T he software

should be written such that the I/O port driving WDI is left in

its power-up reset state until the initialization routines are com-

pleted and the microprocessor is able to toggle WDI at the mini-

mum watchdog timeout period of 70 ms.

8

OSC SEL

NC

ADM8691

ADM8693

ADM8695

7

OSC IN

NC

Figure 4c. Internal Oscillator (1.6 Second Watchdog)

8

OSC SEL

NC

Watchdog O utput (WD O )

T he Watchdog Output WDO (ADM8691/ADM8693/

ADM8695) provides a status output which goes low if the

watchdog timer “times out” and remains low until set high by

the next transition on the Watchdog Input. WDO is also set

high when VCC goes below the reset threshold.

ADM8691

ADM8693

ADM8695

7

OSC IN

Figure 4d. Internal Oscillator (100 m s Watchdog)

8

OSC SEL

ADM8691

ADM8693

ADM8695

CLOCK

0 TO 500kHz

7

OSC IN

Figure 4a. External Clock Source

REV. 0

–7–

ADI [ ADI ]

ADI [ ADI ]