AD9653

Data Sheet

N – 1

VIN±x

N

N + 1

tA

tEH

tEL

CLK–

CLK+

DCO–

tCPD

DDR

SDR

DCO+

DCO

tFCO

tFRAME

FCO–

FCO+

D0–A

tPD

tDATA

BITWISE

MODE

D14

D12

D10

D08

D06

D04

D02

LSB

D14

D12

D10

D08

D06

D04

D02

LSB

N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16

D0+A

D1–A

tLD

MSB

D13

D11

D09

D07

D05

D03

D01

MSB

D13

D11

D09

D07

D05

D03

D01

N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16

D1+A

FCO–

FCO+

D0–A

BYTEWISE

MODE

D07

D06

D05

D04

D03

D02

D01

LSB

D07

D06

D05

D04

D03

D02

D01

LSB

N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16

D0+A

D1–A

MSB

D14

D13

D12

D11

D10

D09

D08

MSB

D14

D13

D12

D11

D10

D09

D08

N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16 N – 16

D1+A

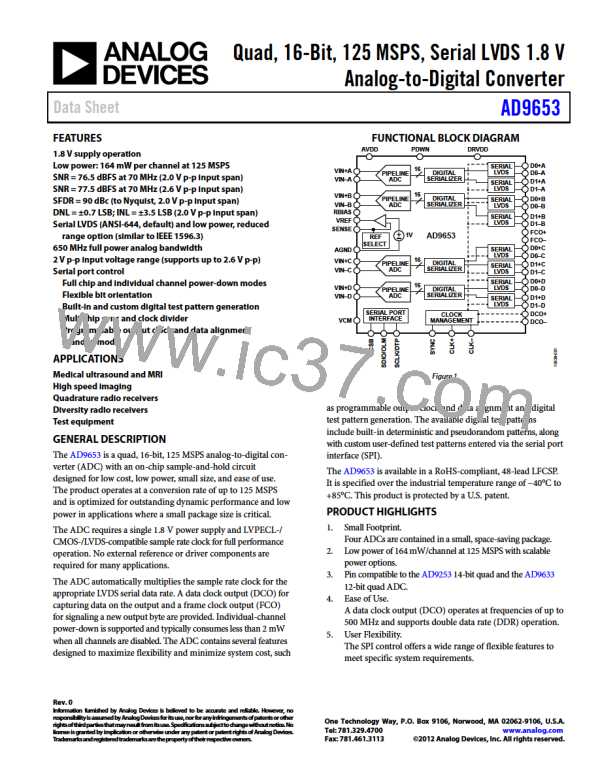

Figure 3. 16-Bit DDR/SDR, Two-Lane, 2× Frame Mode

N – 1

VIN±x

tA

N

tEH

tEL

CLK–

CLK+

tCPD

DCO–

DCO+

tFCO

tFRAME

FCO–

FCO+

tDATA

tPD

D0–x

D0+x

MSB

N – 17

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

LSB

MSB

D14

D13

N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 17 N – 16 N – 16 N – 16

Figure 4. Wordwise DDR, One-Lane, 1× Frame, 16-Bit Output Mode

CLK+

tSSYNC

tHSYNC

SYNC

Figure 5. SYNC Input Timing Requirements

Rev. 0 | Page 10 of 40

ADI [ ADI ]

ADI [ ADI ]