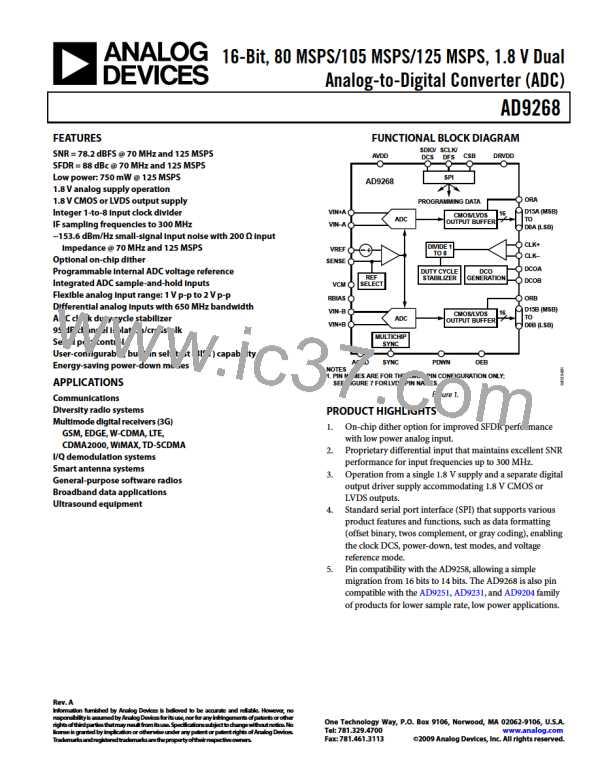

AD9268

PIN 1

INDICATOR

CLK+

CLK–

SYNC

D0– (LSB)

D0+ (LSB)

D1–

1

2

3

4

5

6

7

8

9

48 PDWN

47 OEB

46 CSB

45 SCLK/DFS

44 SDIO/DCS

43 OR+

D1+

D2–

D2+

42 OR–

AD9268

PARALLEL LVDS

TOP VIEW

41 D15+ (MSB)

40 D15– (MSB)

39 D14+

38 D14–

37 DRVDD

36 D13+

35 D13–

34 D12+

33 D12–

DRVDD 10

D3– 11

D3+ 12

D4– 13

D4+ 14

D5– 15

D5+ 16

(Not to Scale)

NOTES

1. THE EXPOSED THERMAL PAD ON THE BOTTOM OF THE PACKAGE

PROVIDES THE ANALOG GROUND FOR THE PART. THIS EXPOSED

PAD MUST BE CONNECTED TO GROUND FOR PROPER OPERATION.

Figure 7. LFCSP Interleaved Parallel LVDS Pin Configuration (Top View)

Table 9. Pin Function Descriptions (Interleaved Parallel LVDS Mode)

Pin No.

Mnemonic

Type

Description

ADC Power Supplies

1±, 19, 28, 3ꢁ

DRVDD

AVDD

Supply

Supply

Digital Output Driver Supply (1.8 V Nominal).

Analog Power Supply (1.8 V Nominal).

49, ꢀ±, ꢀ3, ꢀ4, ꢀ9,

6±, 63, 64

±

AGND,

Exposed Pad

Ground

The exposed thermal pad on the bottom of the package provides the analog

ground for the part. This exposed pad must be connected to ground for proper

operation.

ADC Analog

ꢀ1

ꢀ2

62

61

VIN+A

VIN−A

VIN+B

VIN−B

VREF

Input

Input

Input

Input

Differential Analog Input Pin (+) for Channel A.

Differential Analog Input Pin (−) for Channel A.

Differential Analog Input Pin (+) for Channel B.

Differential Analog Input Pin (−) for Channel B.

ꢀꢀ

Input/Output Voltage Reference Input/Output.

ꢀ6

ꢀ8

ꢀꢁ

1

SENSE

RBIAS

VCM

CLK+

CLK−

Input

Voltage Reference Mode Select. See Table 11 for details.

Input/Output External Reference Bias Resistor.

Output

Input

Common-Mode Level Bias Output for Analog Inputs.

ADC Clock Input—True.

ADC Clock Input—Complement.

2

Input

Digital Input

3

SYNC

Input

Digital Synchronization Pin. Slave mode only.

Digital Outputs

ꢀ

4

ꢁ

6

9

8

12

D±+ (LSB)

D±− (LSB)

D1+

D1−

D2+

Output

Output

Output

Output

Output

Output

Output

Channel A/Channel B LVDS Output Data ±—True.

Channel A/Channel B LVDS Output Data ±—Complement.

Channel A/Channel B LVDS Output Data 1—True.

Channel A/Channel B LVDS Output Data 1—Complement.

Channel A/Channel B LVDS Output Data 2—True.

Channel A/Channel B LVDS Output Data 2—Complement.

Channel A/Channel B LVDS Output Data 3—True.

D2−

D3+

Rev. A | Page 1ꢀ of 44

ADI [ ADI ]

ADI [ ADI ]