EM73P362

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

WATCH-DOG-TIMER ( WDT )

Watch-dog-timer can help user to detect the malfunction (runaway) of CPU and give system a time up

signal every certain time. User can use the time up signal to give system a reset signal when system is fail.

This function is available by mask option. If the mask option of WDT is enabled, it will stop counting when

CPU is reseted or in the STOP operation mode.

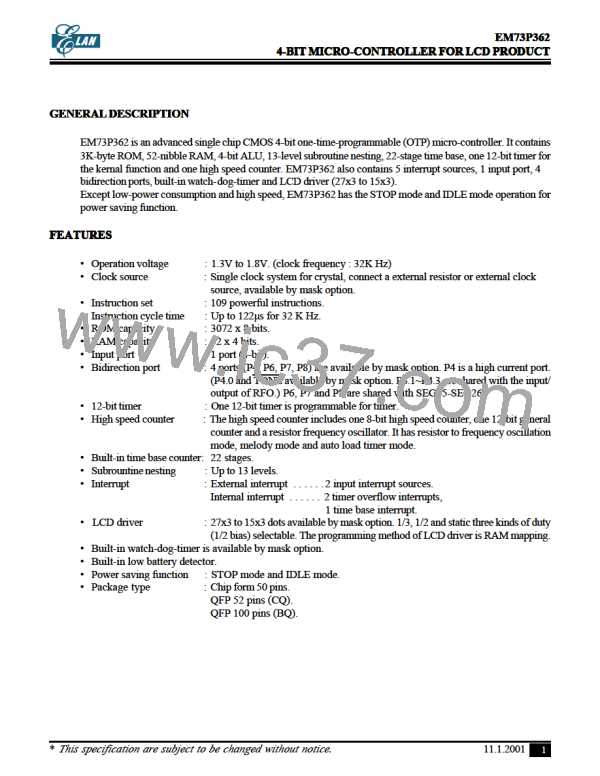

The basic structure of watch-dog-timer control is composed by a 4-stage binary counter and a control unit.

The WDT counter counts for a certain time to check the CPU status, if there is no malfunction happened,

the counter will be cleared and counting. Otherwise, if there is a malfunction happened, the WDT control

will send a WDT signal (low active) to reset CPU. The WDT checking period is assign by P21 (WDT

command port).

WDT counter

13

XIN / 2

0

1

2

3

RESET pin

mask option

WDT control

counter clear request

P21

WDT

command port

P21 is the control port of watch-dog-timer, and the WDT time up signal is connected to RESET.

P21

3

2

1

0

Initial value : 0000

CWC *

*

WDT

CWC

0

1

Clear watch-dog-timer counter

Clear counter then return to 1

Nothing

WDT

0

1

Set watch-dog-timer detect time

3 x 213/XIN = 3 x 213/32K Hz = 0.75 sec

7 x 213/XIN = 7 x 213/32K Hz = 1.75 sec

PROGRAM EXAMPLE

To enable WDT with 7 x 213/XIN detection time.

LDIA

OUTA

#0001B

P21

;set WDT detection time and clear WDT counter

:

:

* This specification are subject to be changed without notice.

11.1.2001

27

ELAN [ ELAN MICROELECTRONICS CORP ]

ELAN [ ELAN MICROELECTRONICS CORP ]